Kernel Studio dev progress

https://risc-v-getting-started-guide.readthedocs.io/en/latest/linux-qemu.html Running 64- and 32-bit RISC-V Linux on QEMU This is a “hello world” example of booting Linux on RISC-V QEMU. This guide covers some basic steps to get Linux running on RISC-V. It is recomended that if you are interested in a specific distrubution you follow their steps. For example if you are interested […]

我地平時用嘅variable,如果化到落logic gate呢一層,你無法找到佢嘅真身,佢亦都好可能同其它variable所化生嘅logic gate交織埋一齊,你亦都無可能找到佢確實嘅存在嘅時間,一切好虛無,但有其功用。呢個係coding體驗空性嘅其中一個睇法。而家啲programmer執著玩排位玩放位玩lang玩framework,真係好可憐。

Learn more advanced skills for sharepoint tuning from sql server point of view.

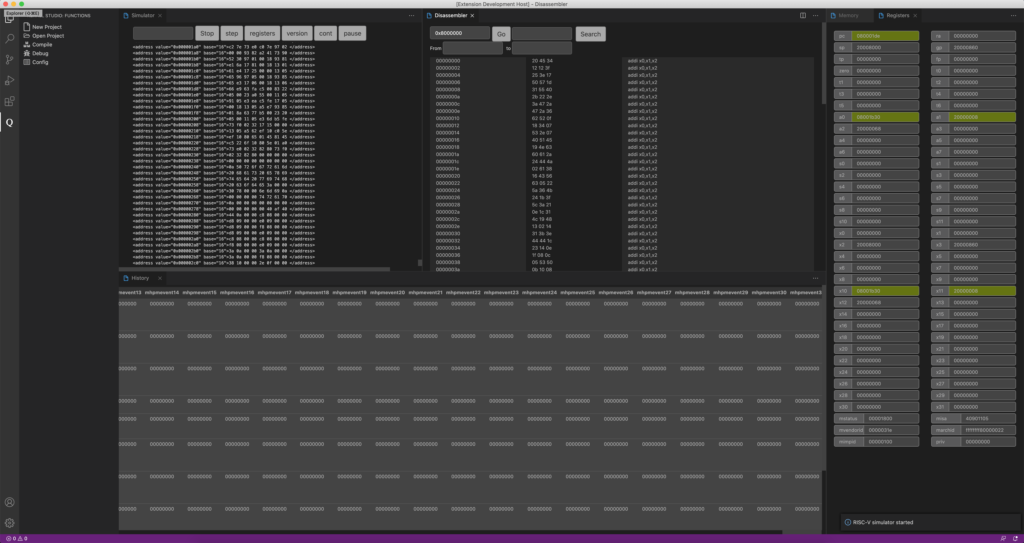

===== RISC-V Registers(0) zero (/32)(1) ra (/32)(2) sp (/32)(3) gp (/32)(4) tp (/32)(5) t0 (/32)(6) t1 (/32)(7) t2 (/32)(8) fp (/32)(9) s1 (/32)(10) a0 (/32)(11) a1 (/32)(12) a2 (/32)(13) a3 (/32)(14) a4 (/32)(15) a5 (/32)(16) a6 (/32)(17) a7 (/32)(18) s2 (/32)(19) s3 (/32)(20) s4 (/32)(21) s5 (/32)(22) s6 (/32)(23) s7 (/32)(24) s8 (/32)(25) s9 (/32)(26) […]

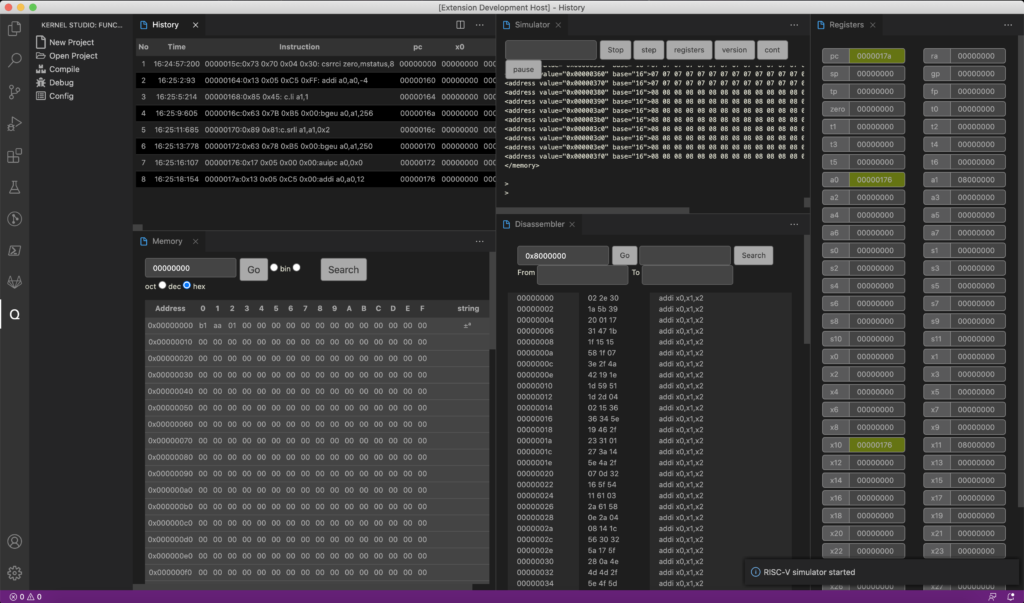

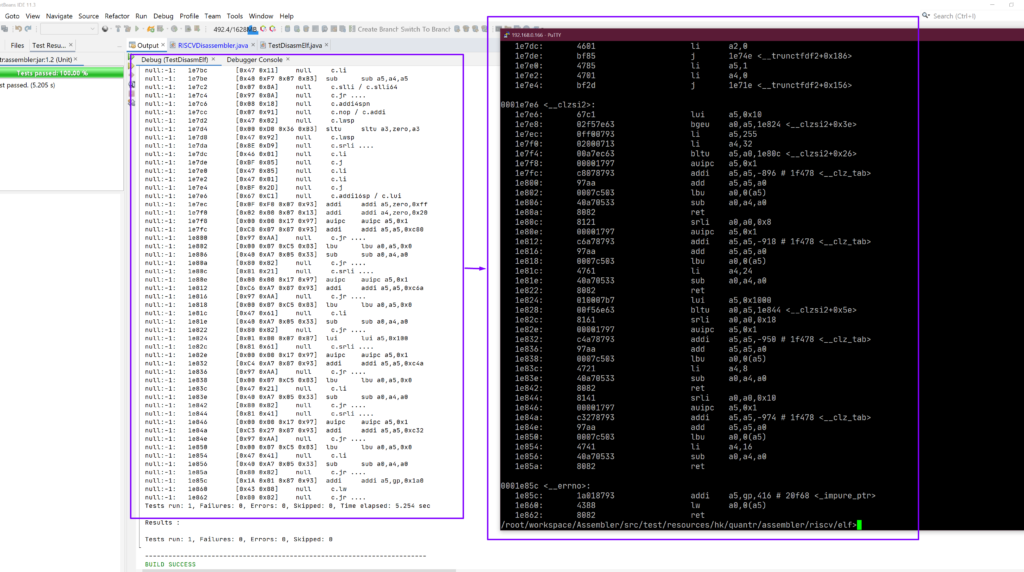

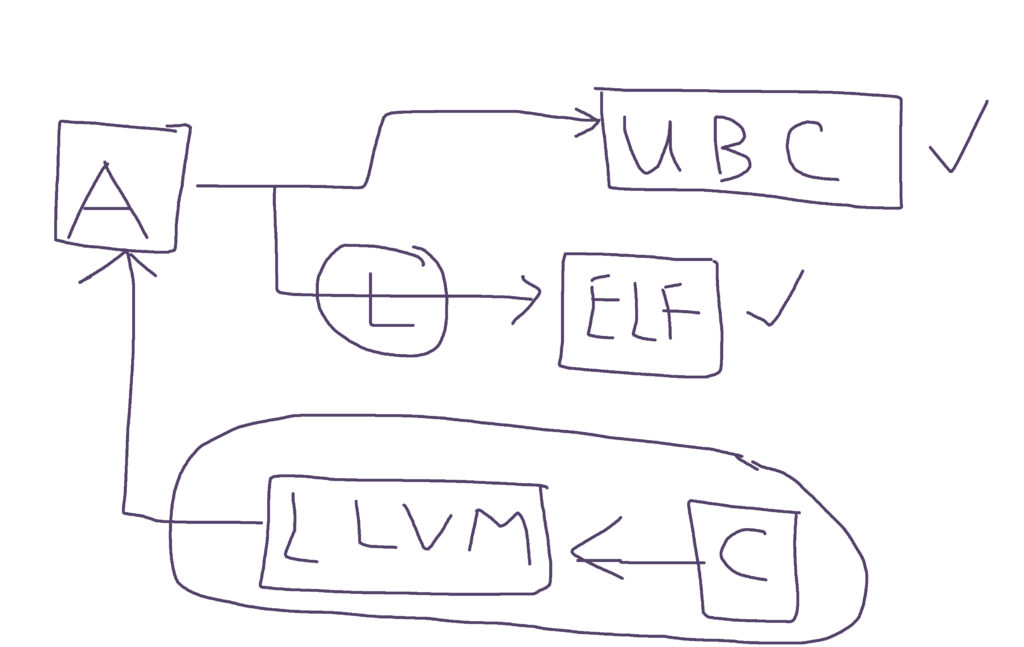

We have good progress, finished running 3 examples successfully. Go jump in to simulate some big examples.

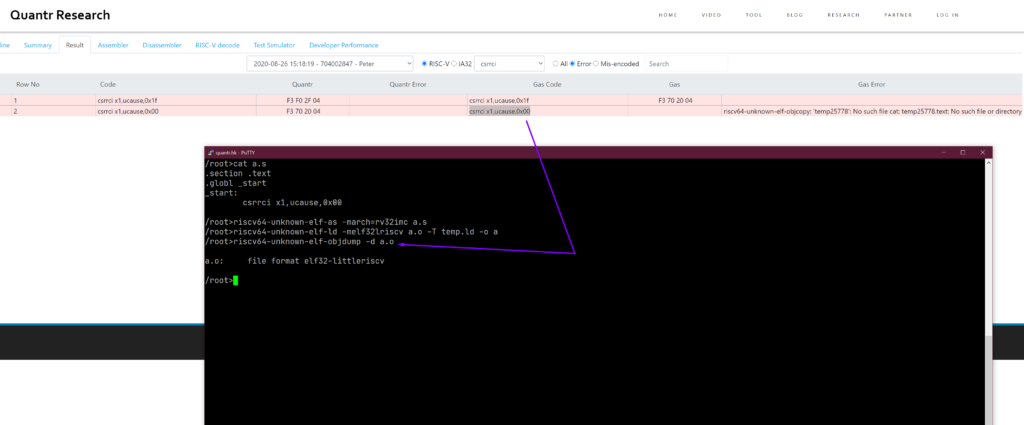

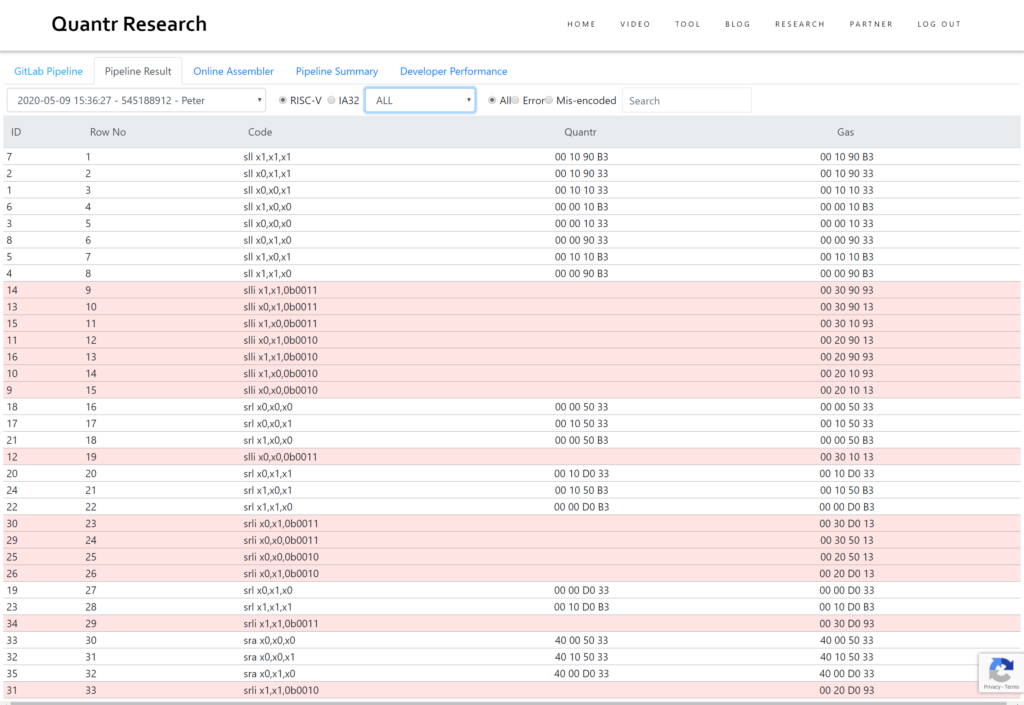

Compiling instruction “csrrci x1,ucause,0x00” produce no bytes

https://www.mssqltips.com/sqlservertip/3889/resolving-sharepoint-application-authentication-error-login-failed/

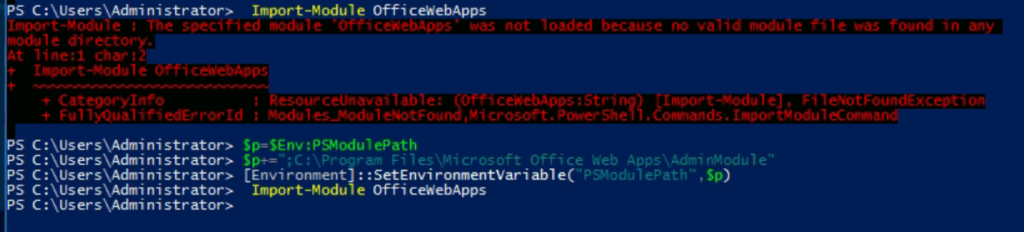

This will fix the problem:

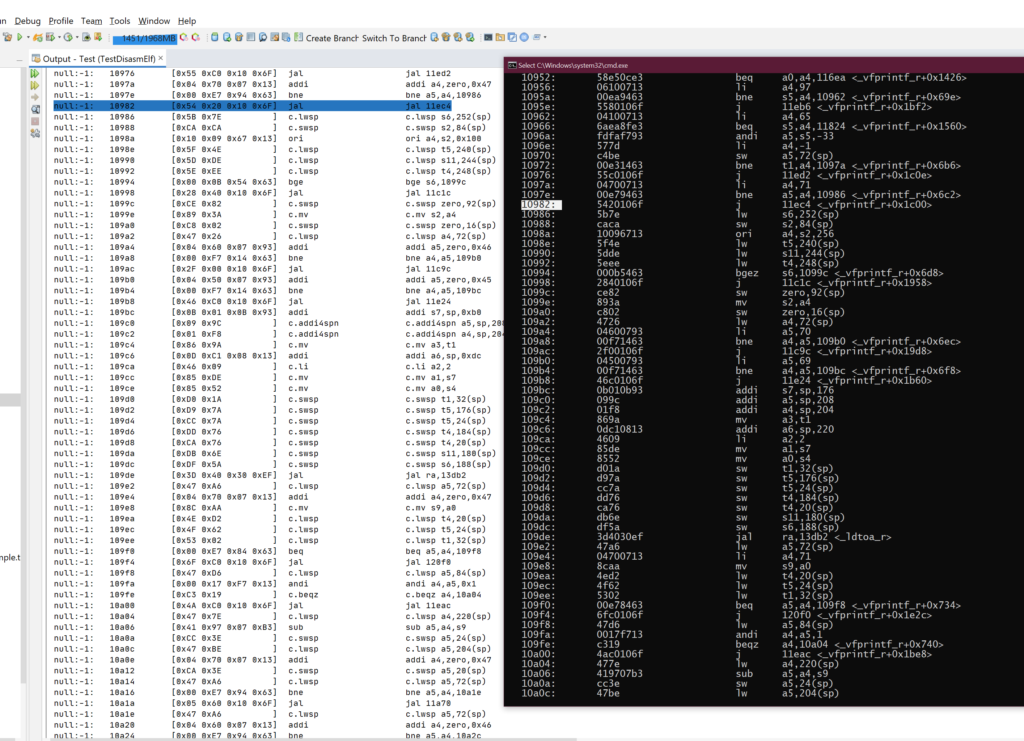

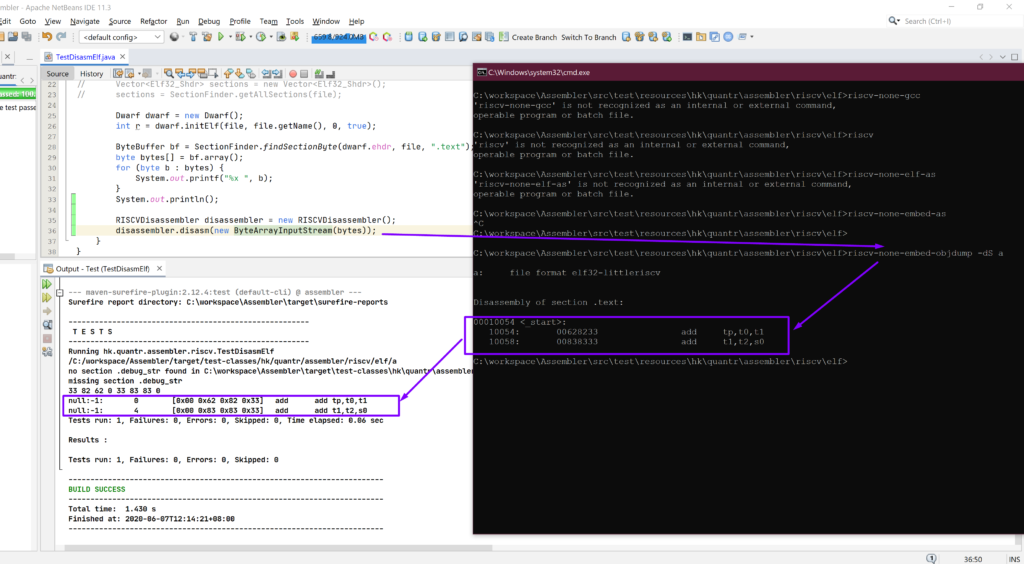

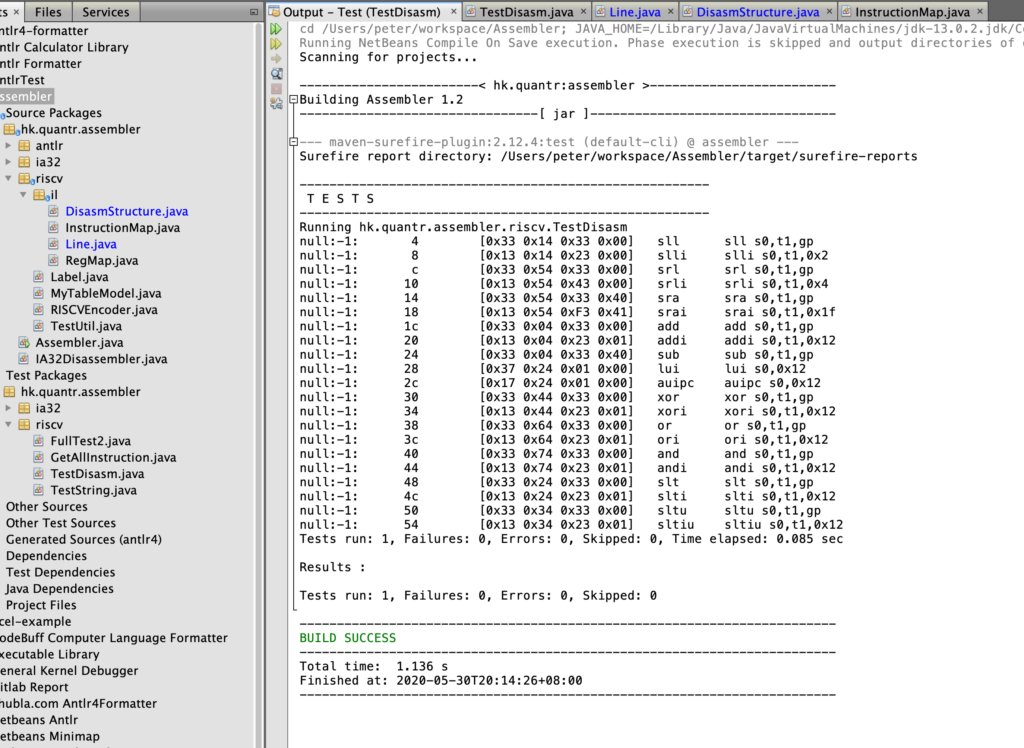

RISC-V encoding part & decoding part of assembler and disassembler for imc are done.

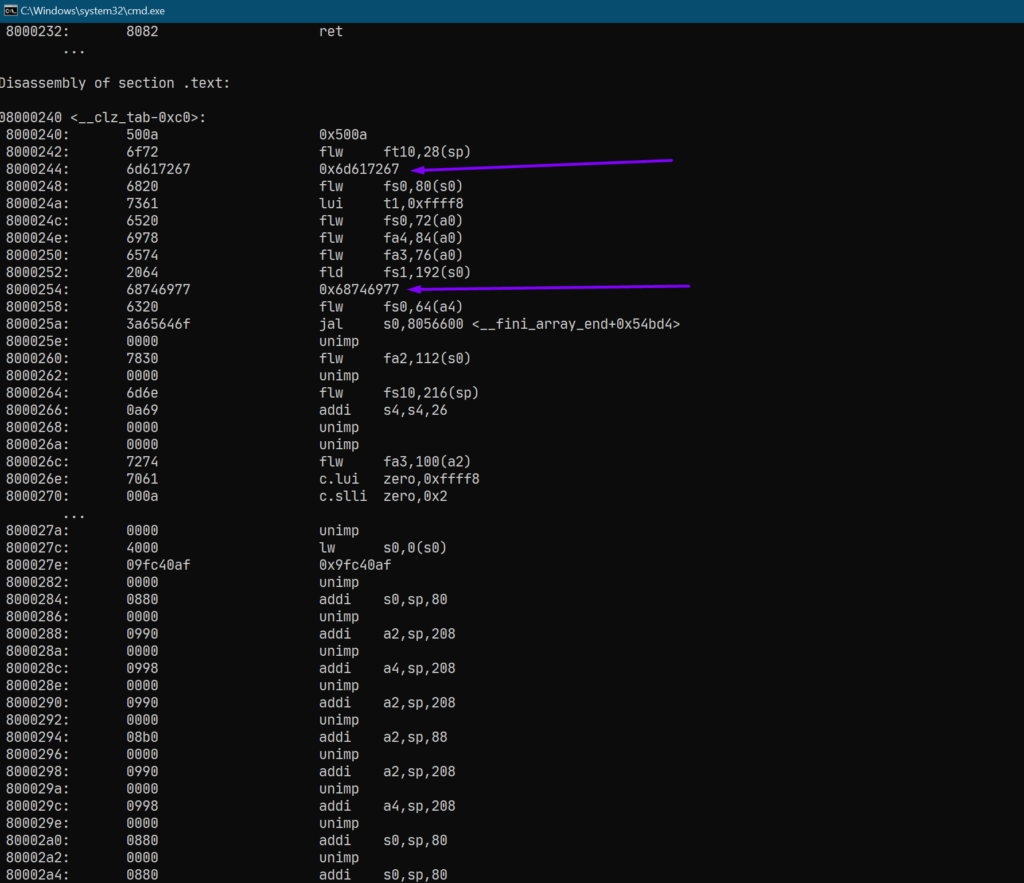

I think i can finish the RISC-V disassembler these two weeks. So far it can successfully decode RV32IC and ELF.

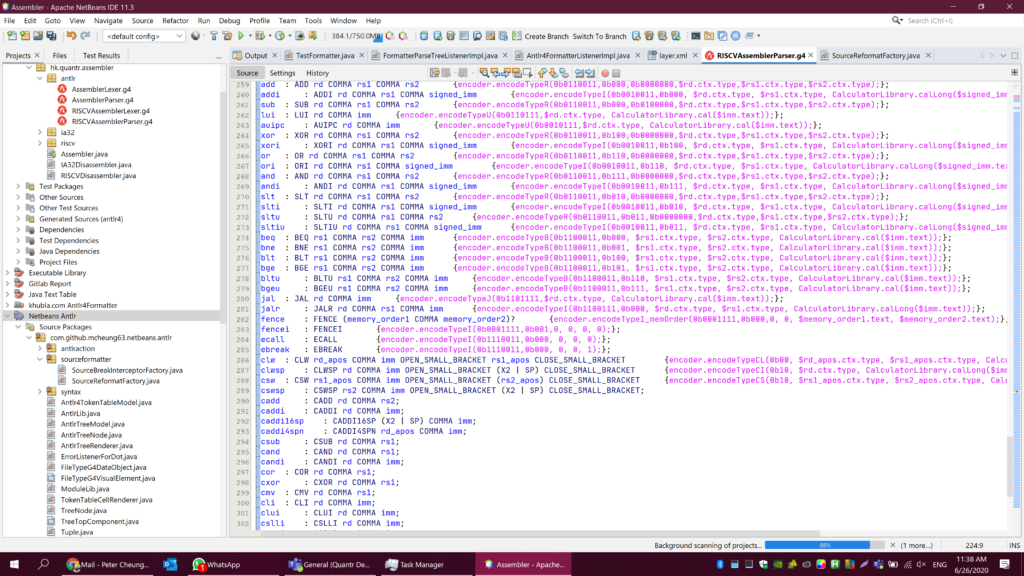

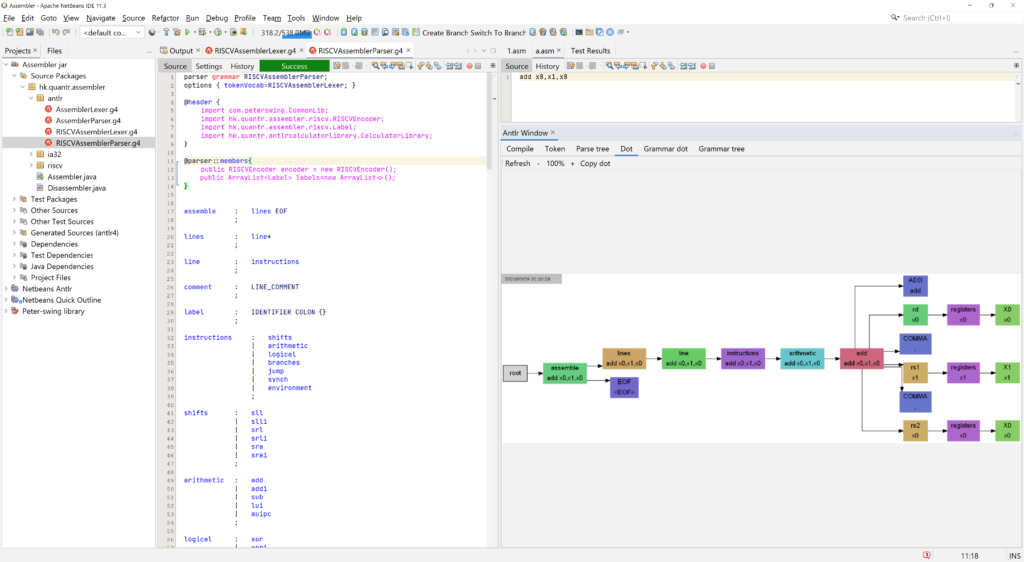

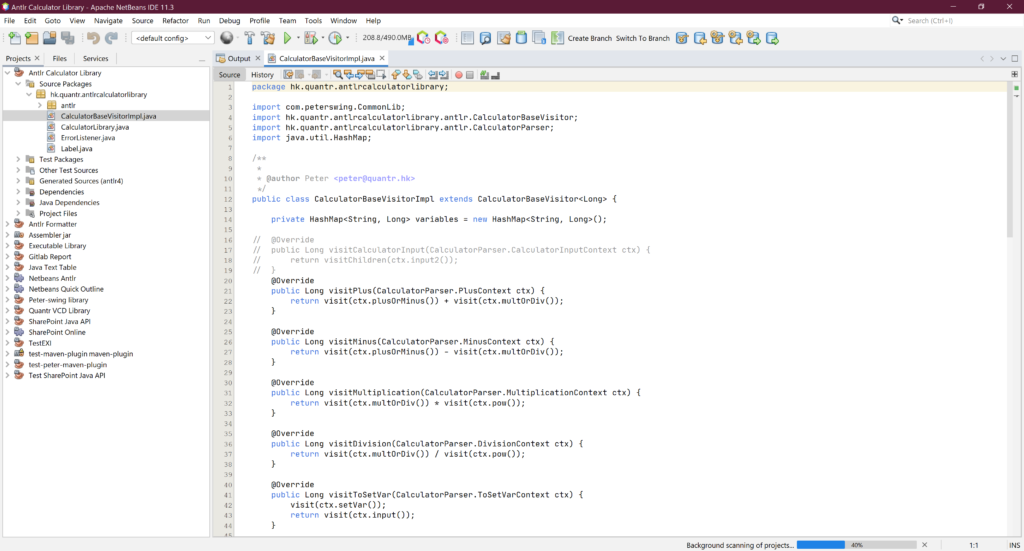

My netbeans antlr plugin finally can format antlr source code

c.sub should be CA format, not CR

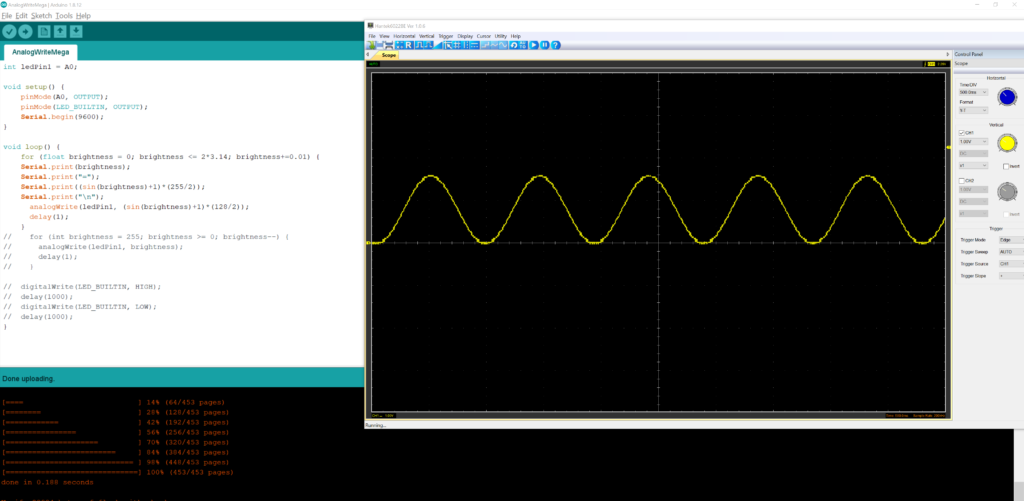

My Arduino board has built-in DAC, can output sine wave.

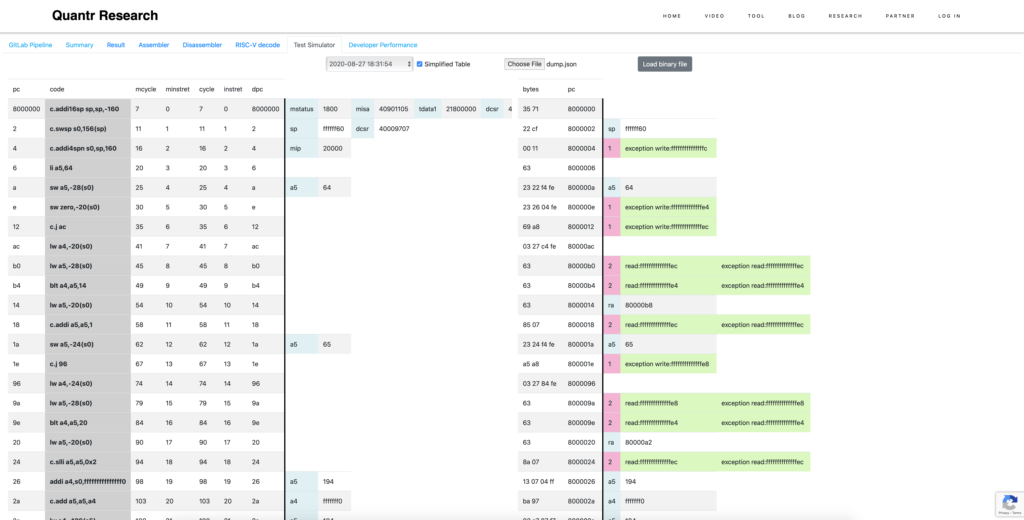

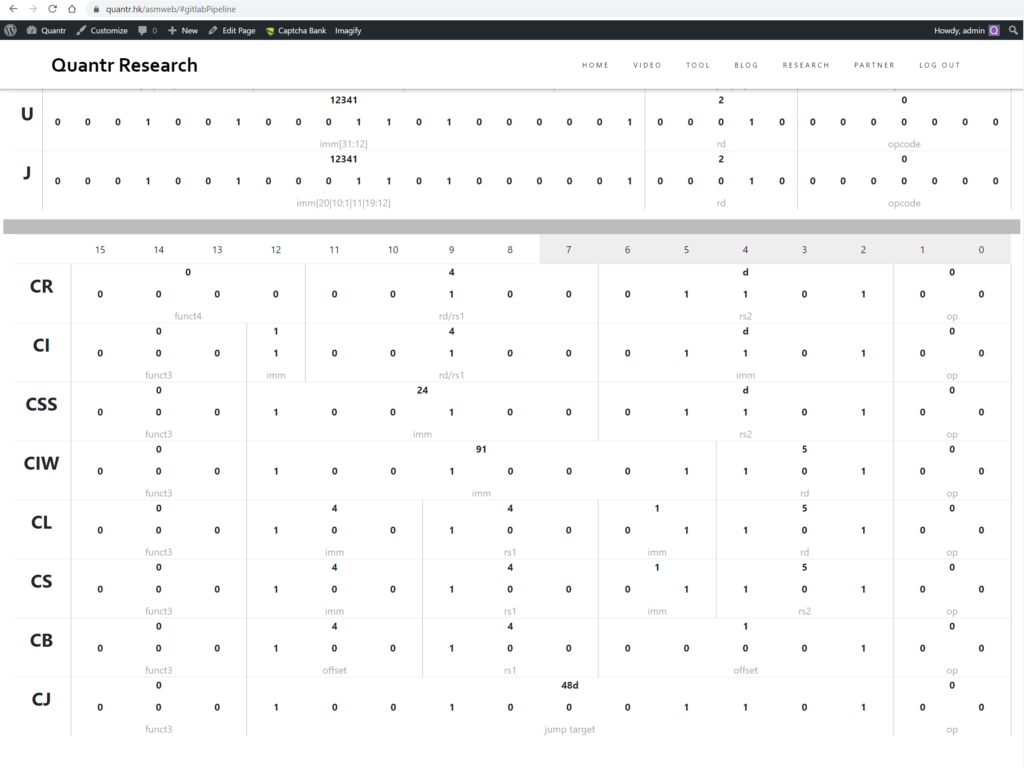

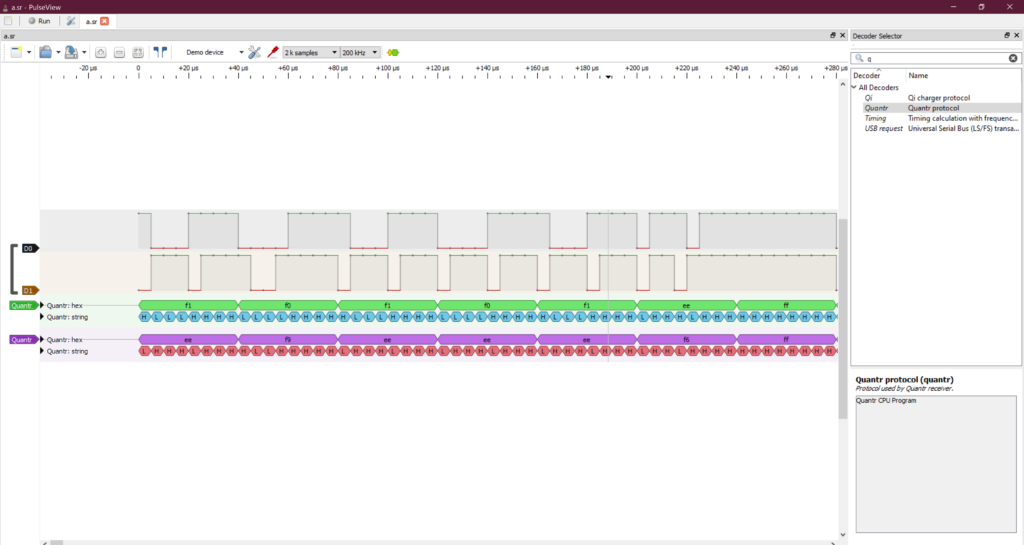

Doing RISC-V assembler, this is our first decode screen

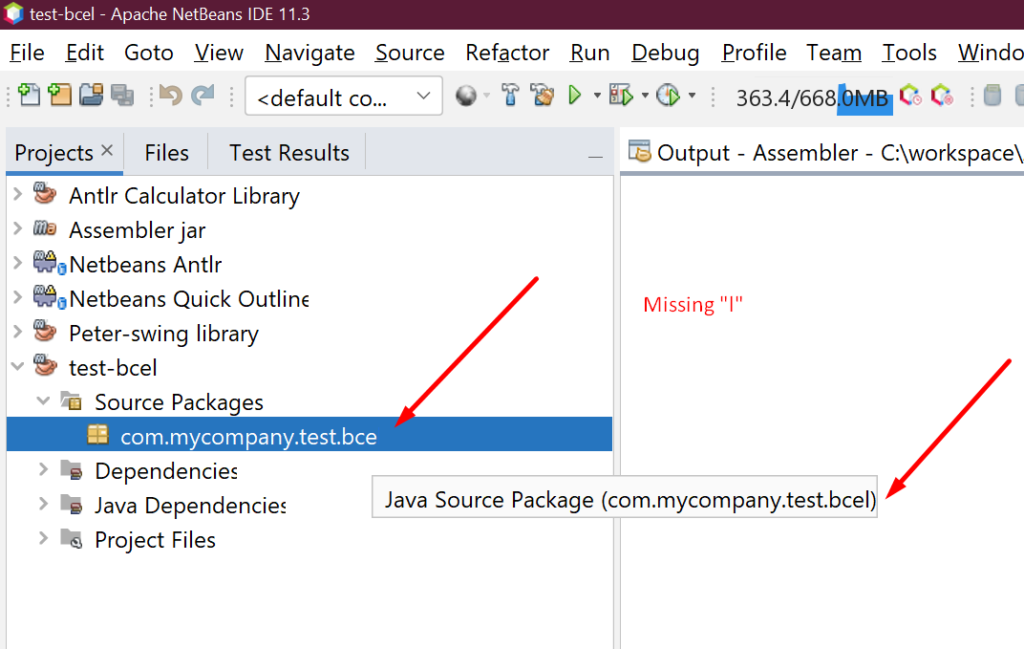

Netbeans 11.3 + JDK 13.0.2 + FlatLaf Light theme. Missing character “l” in the package name. If mouse over, tooptip shows correct name.

Pnp provision framework has these steps: 01/20 – Regional Settings02/20 – Supported UI Languages03/20 – Audit Settings04/20 – Site Security05/20 – Fields06/20 – Content Types07/20 – List instances08/20 – Features09/20 – Page Contents10/20 – Client Side Page Contents11/20 – Site Header12/20 – Site Footer13/20 – Property bag entries14/20 – Workflows15/20 – Web Settings16/20 – Site […]

Used near 6 hours to fix my netbeans-antlr plugin. I have to remember these: Netbeans build in antlr library have to in-sync with the antlr i am using in my pluging. If they in different version, unexpected result will come out. In windows, if antlr grammar has some mistakes (I meant not problems, your grammar […]

added RISC-V supports to our testbench portal

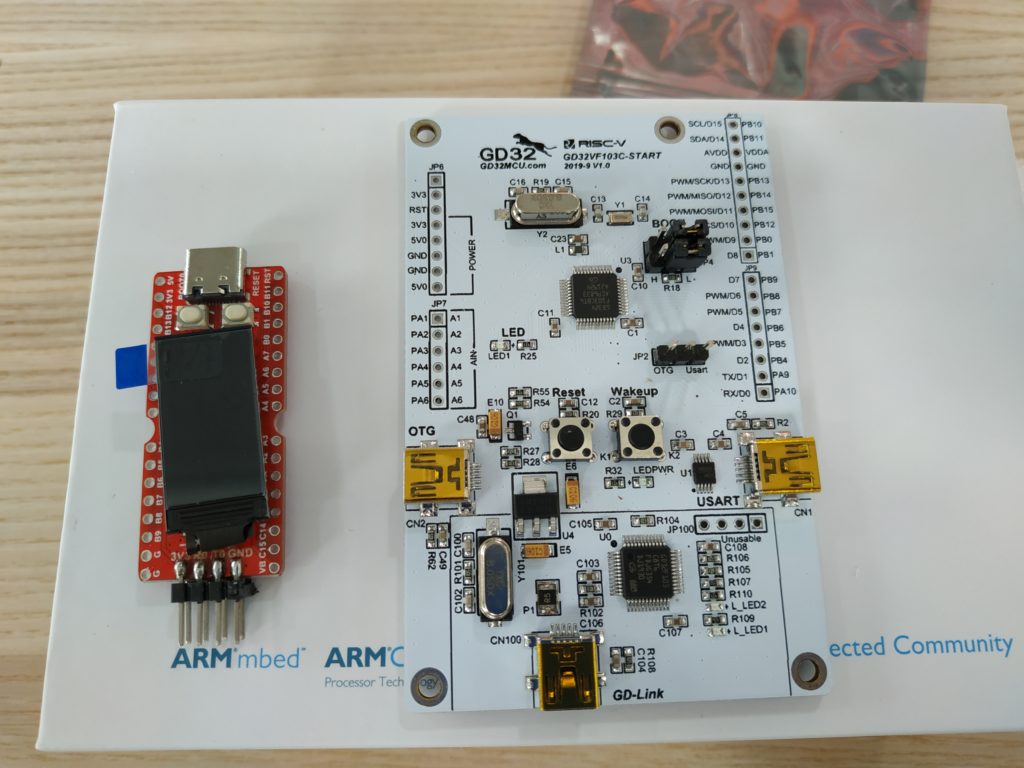

Let’s do some real experiments on these boards: https://item.taobao.com/item.htm?spm=a230r.1.14.201.65363b3cWNnt8y&id=609421832198&ns=1&abbucket=1#detail https://item.taobao.com/item.htm?spm=a230r.1.14.213.65363b3cWNnt8y&id=606277334580&ns=1&abbucket=1#detail

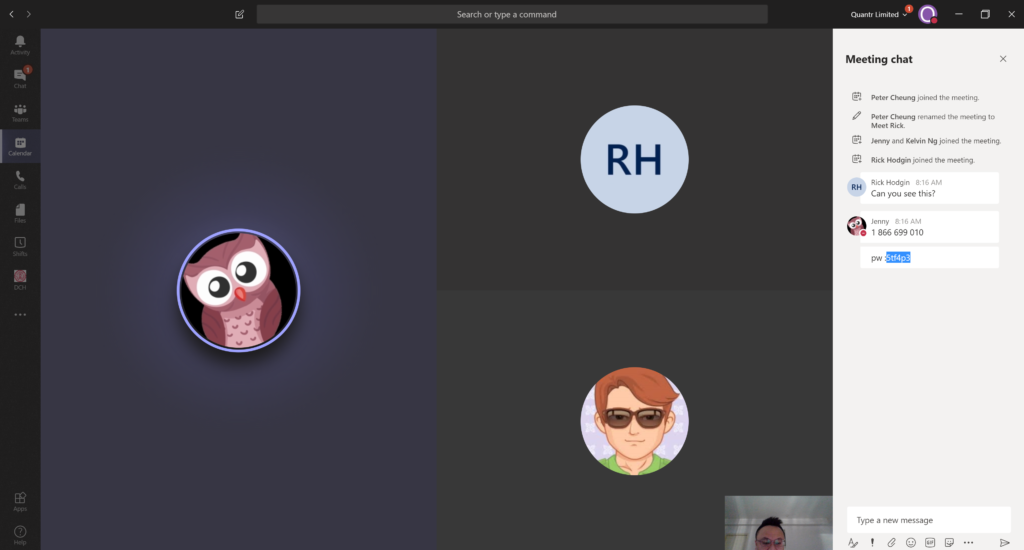

2020/04/30. Our assembler team met Rick, Rick is come from America, our first team member from USA. Jenny shown her about the assembler design and Rick share his opinions about the UBC.

https://www.cnblogs.com/liuxianan/p/vscode-plugin-common-api.html

We agreed to put x86 and risc-v assembler code into one project, so up one level for the java package, make it ready to stuck in risc-v code I will write the first risc-v assembly grammar and upgrade www.quantr.hk/asmweb to support risc-v test cases Learning vscode extension development, make myself ready to create a debugger […]

Only 42 instructons are wrong. We are close to first milestone. Will study “Island Grammar”, hope it is the way to embed other antlr grammar from the main one.