Category Archives: Computer Engineering

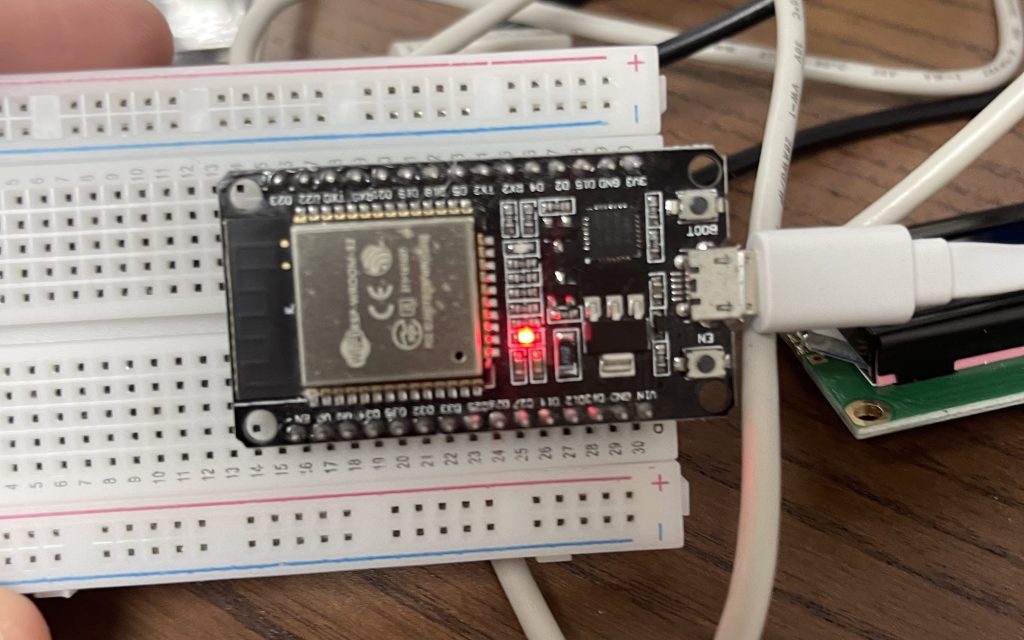

ESP32 on arduino, simplest tutorial

Got this board from Taobao. Follow https://randomnerdtutorials.com/installing-the-esp32-board-in-arduino-ide-windows-instructions. schematic:https://pan.baidu.com/s/1sNCK3Z4ZXfziKoF-ZYDMiw Code:pxc4doc:https://pan.baidu.com/s/1SJFlgyIenaM4-TfmT1eLtQ Code:NICE or download here If you failed to run the code for this. Hold "Boot" button while uploading the code If you meet "the port doesn't exist", do: 2023/04/27

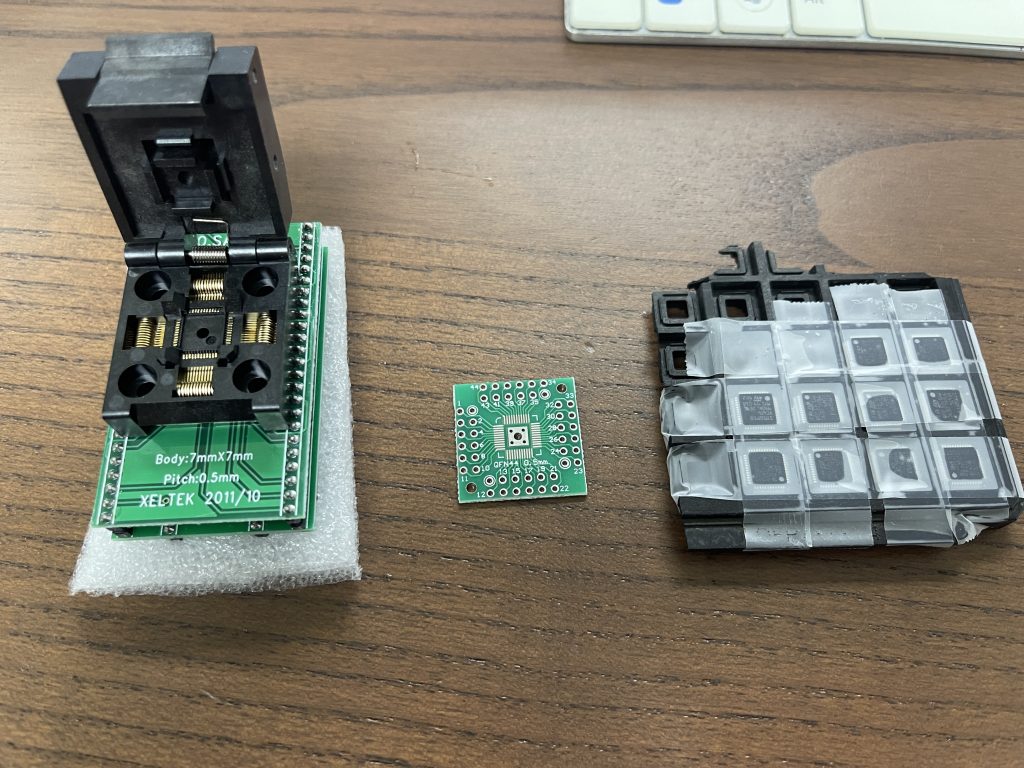

STM32 - 自古成功在嘗試

STM32FEBKC6T6 2023/04/21

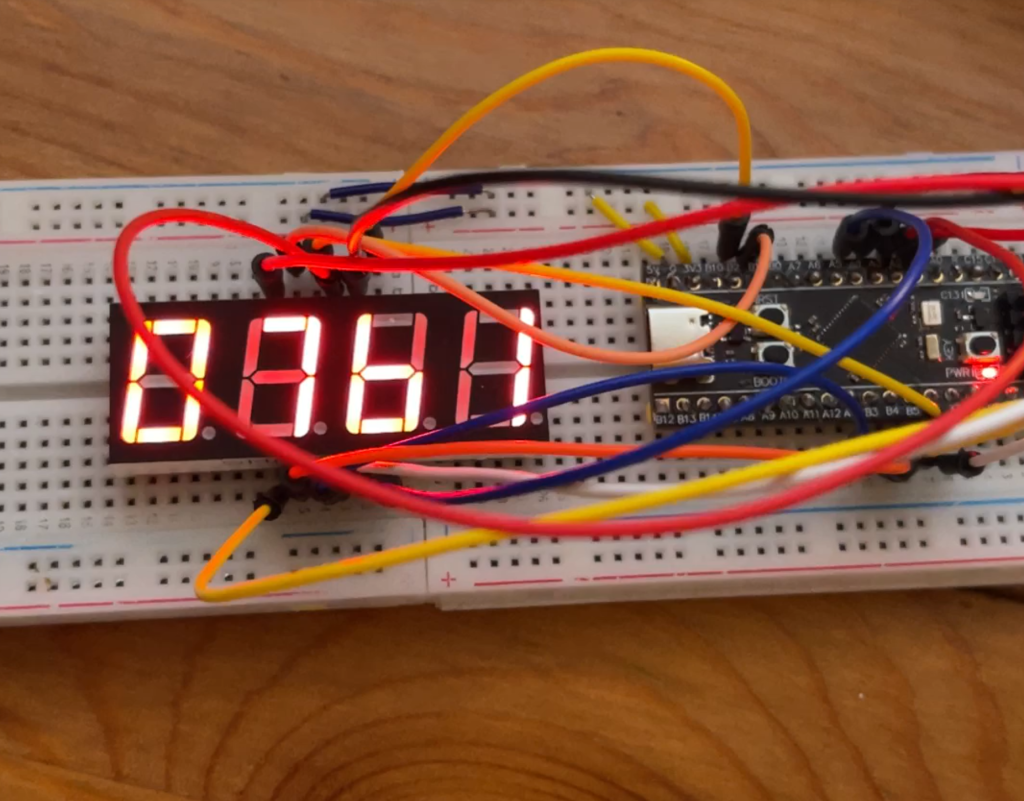

STM32 controls 4 digits 8 segment led

MyFunction.c Control Code 2023/04/20

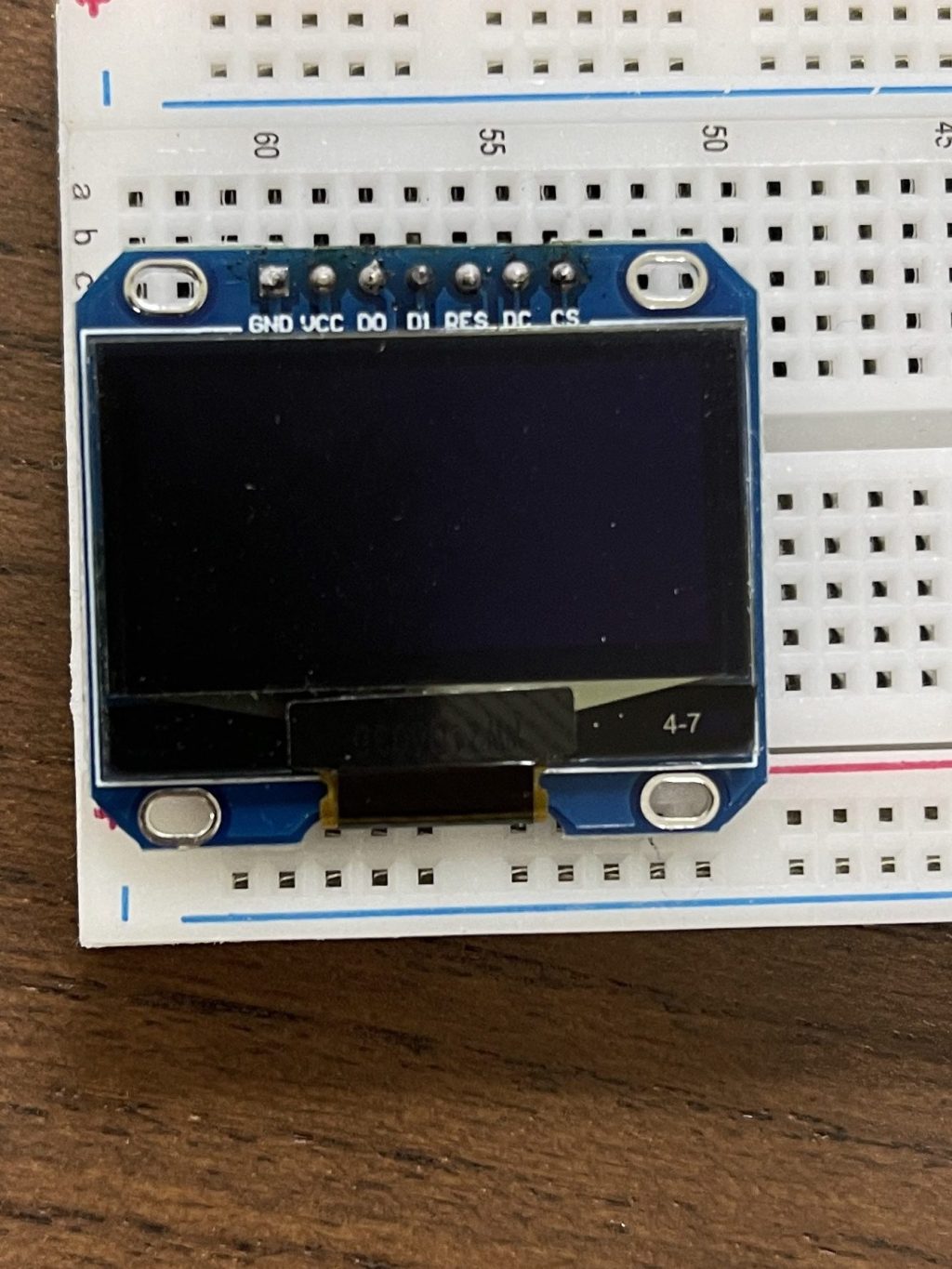

01.54 OLED with STM32 example (7 pins)

Buy from here. Example is in here 2023/04/18

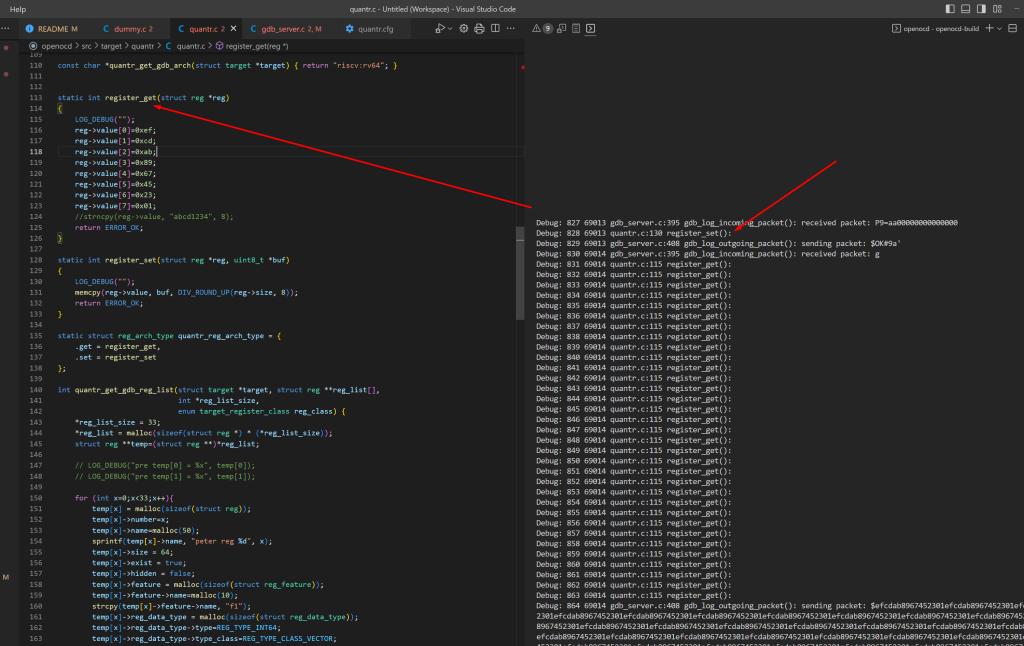

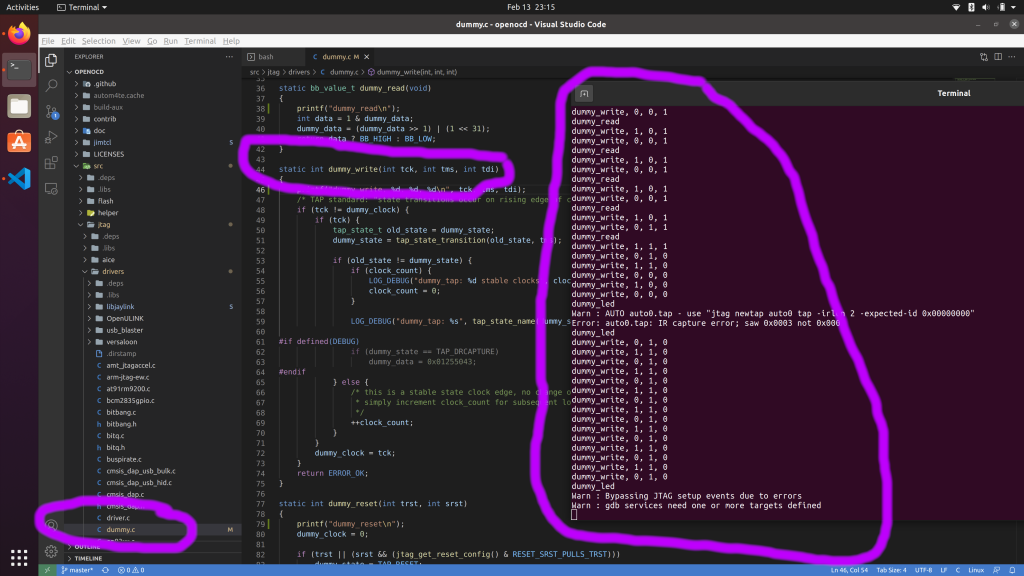

Create a dummy driver for openocd

We are developing our own risc-v so we need to have to ability to modify openocd. Here is the quickest guide for you to start when you type "set $s1=0xaabb", it will jump to here 2023/04/12

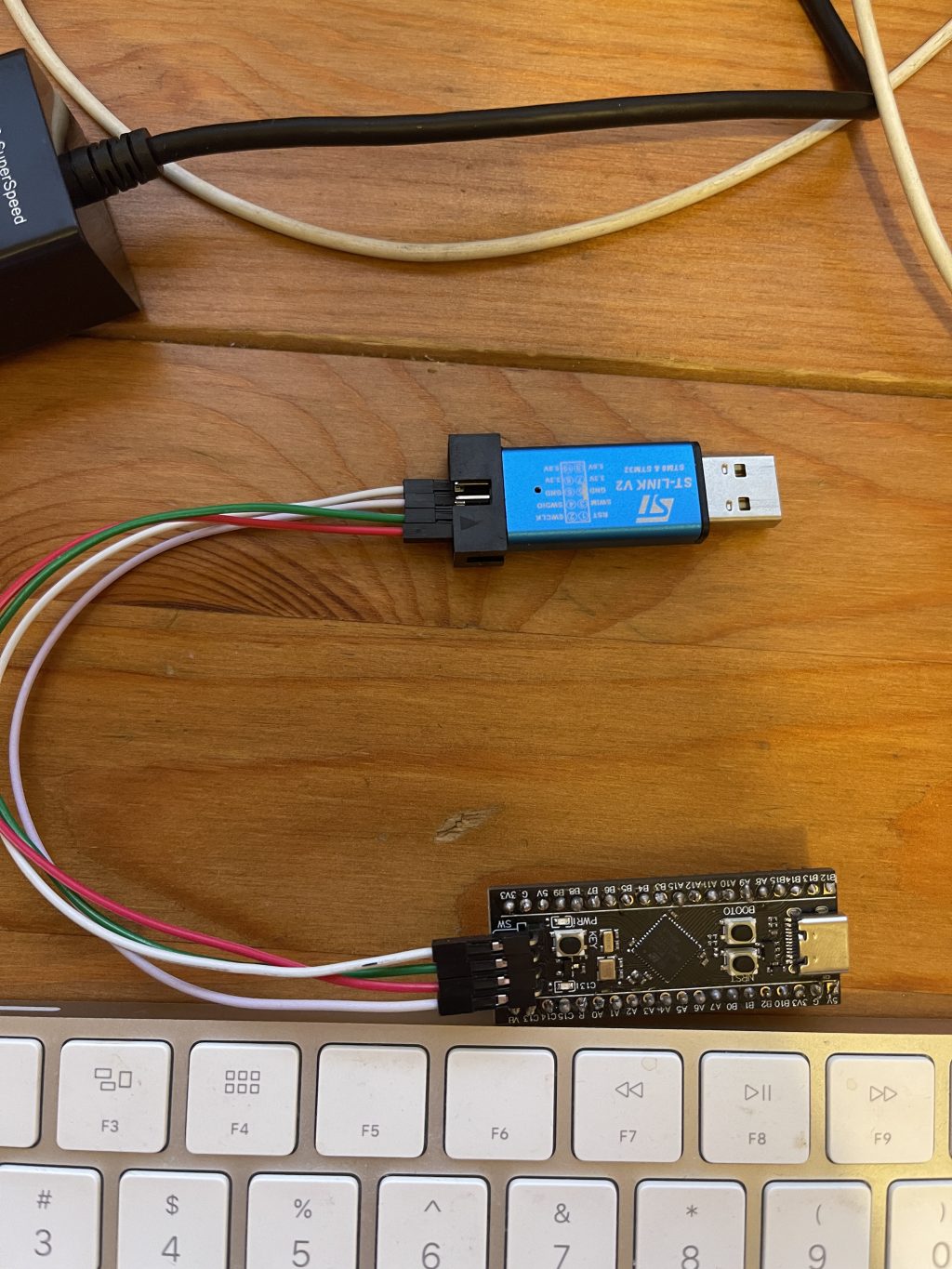

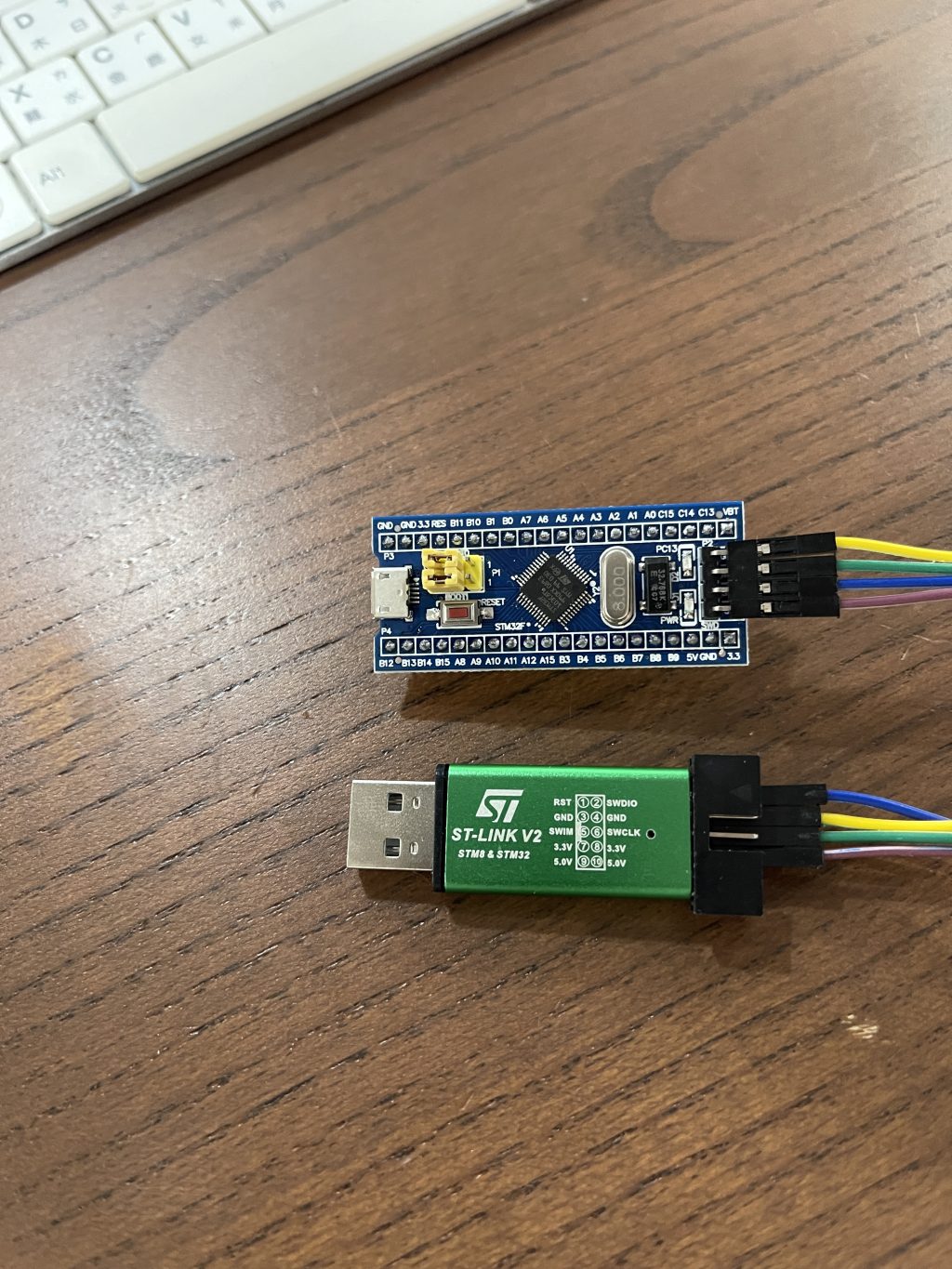

Very small STM32 board

Buy from here https://item.taobao.com/item.htm?spm=a1z09.2.0.0.67002e8deFDqTo&id=630403001847&_u=bbuhab0778e , model is STM32F103C8T6 2023/04/11

Basic tutorial for blinking led for STM32F411

Tutorial: Create the project Step 1: Open STM32IDE, create the project, choose the right MCU Step 2: Type in project name Step 3: This is project structure Step 4: LED is assign to PC13, set it to GPIO output Then it will generate the setup code Step 5: Blink the led in main, there is […] 2023/04/08

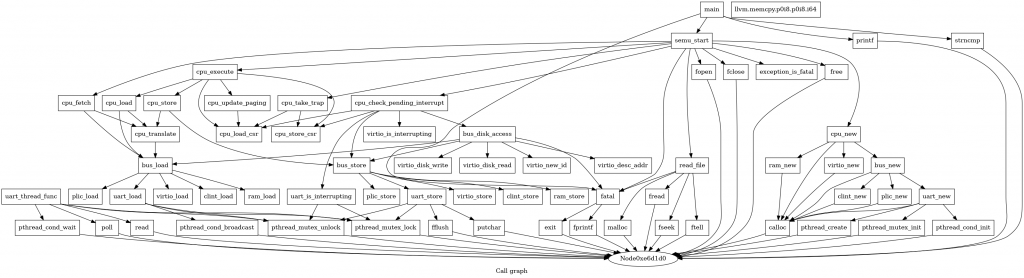

SEMU call graph

This graph generated by graphviz, helping students easier understand Professor Jim Huang's SEMU RISC-V emulator 2023/02/27

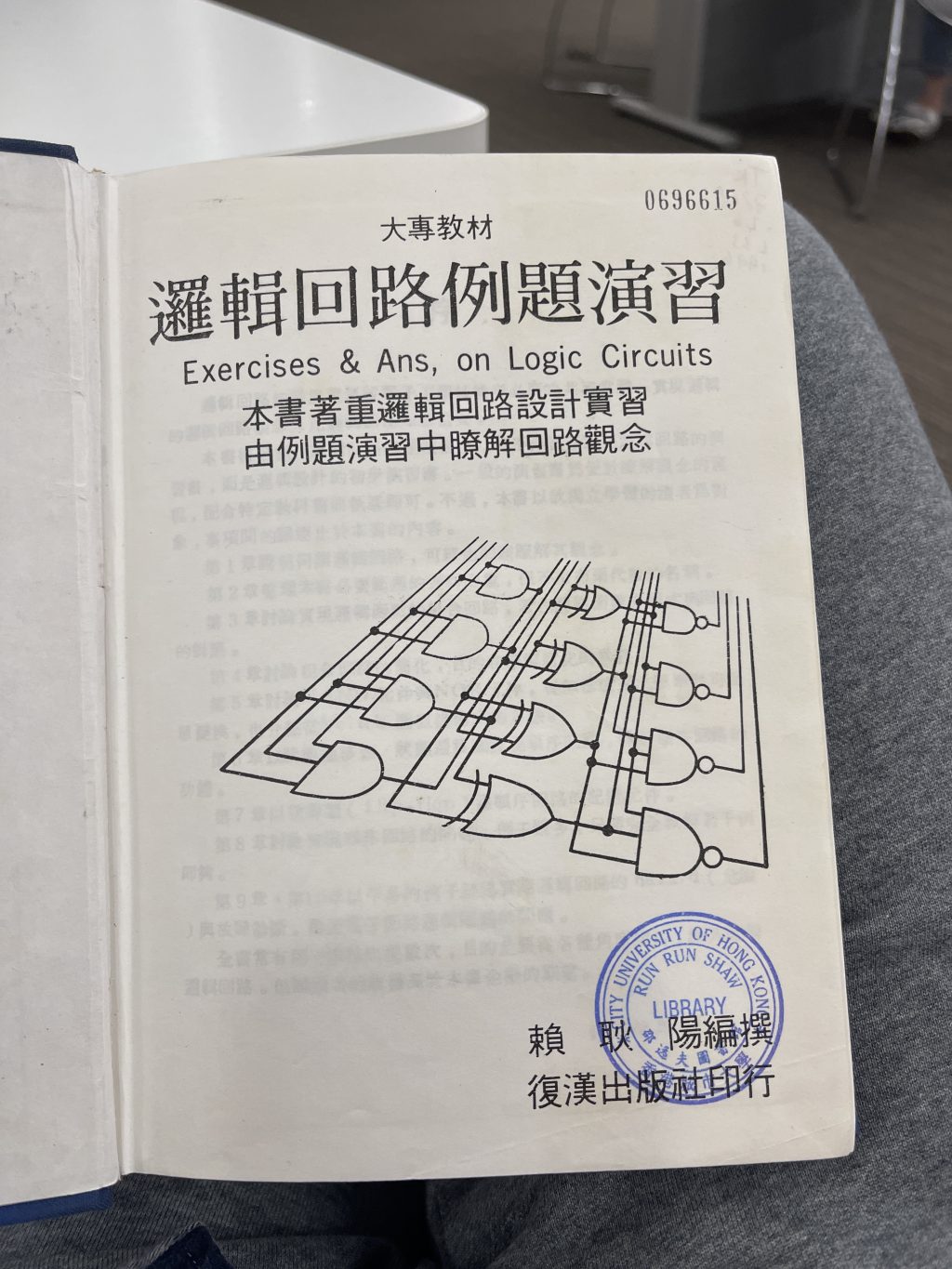

好正嘅一本Logic書

講得好step by step 2023/02/10

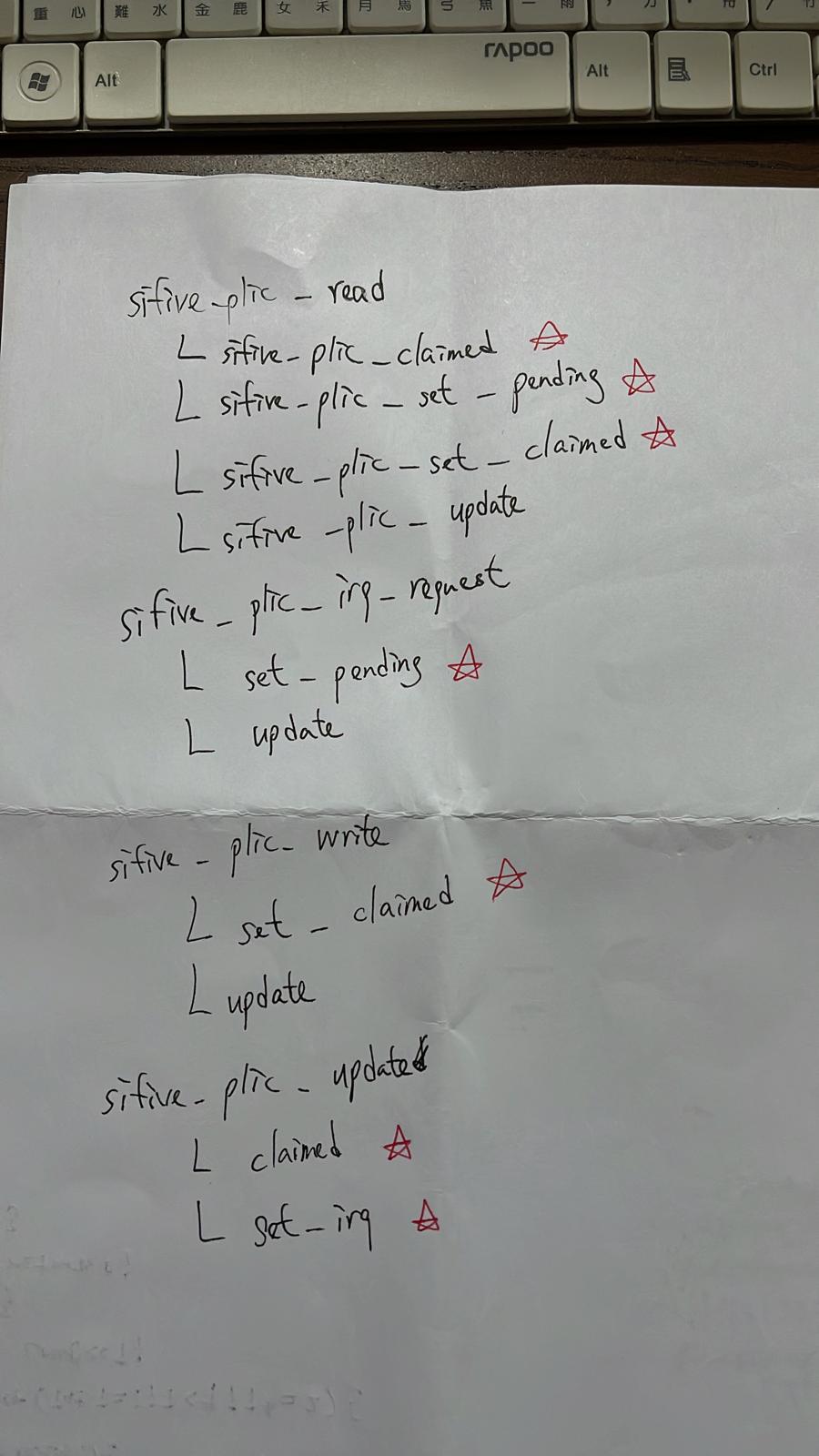

QEMU PLIC call map

After hacking the qemu risc-v source code, here is the PLIC call map 2023/02/06

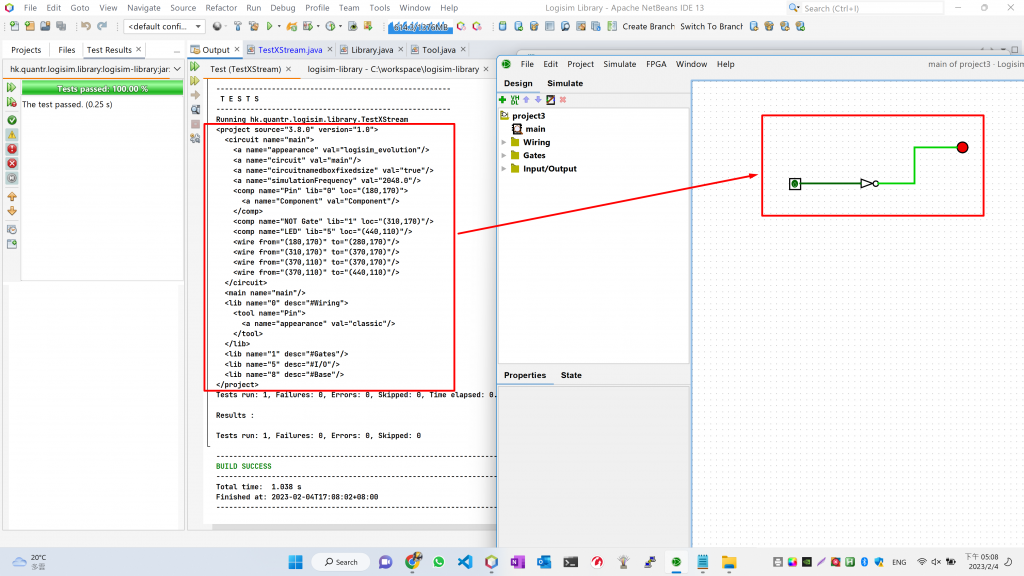

Export our data structure into logisim

Created the library to export our data structure into logisim, https://gitlab.com/quantr/eda/logisim-library , part of our EDA tool 2023/02/04

Good HDL synthesis book

The first step of logic synthesis is call "HDL synthesis", converting verilog into raw netlist. http://ebook.pldworld.com/_eBook/FPGA%EF%BC%8FHDL/-Eng-/Verilog%20HDL%20Synthesis.%20A%20Practical%20Primet%20%28Bhasker%29.pdf 2023/02/01

Good book on logic synthesis

These two papers are referenced by above book about HDL translator 2023/01/29

Cadence Install Guide

https://downloadly.net/2020/19/7490/03/cadence-ic/23/?#/7490-cadence-212315010314.htmlhttps://downloadly.net/2020/19/7490/03/cadence-ic/23/?#/7490-cadence-212315010314.html 2023/01/19

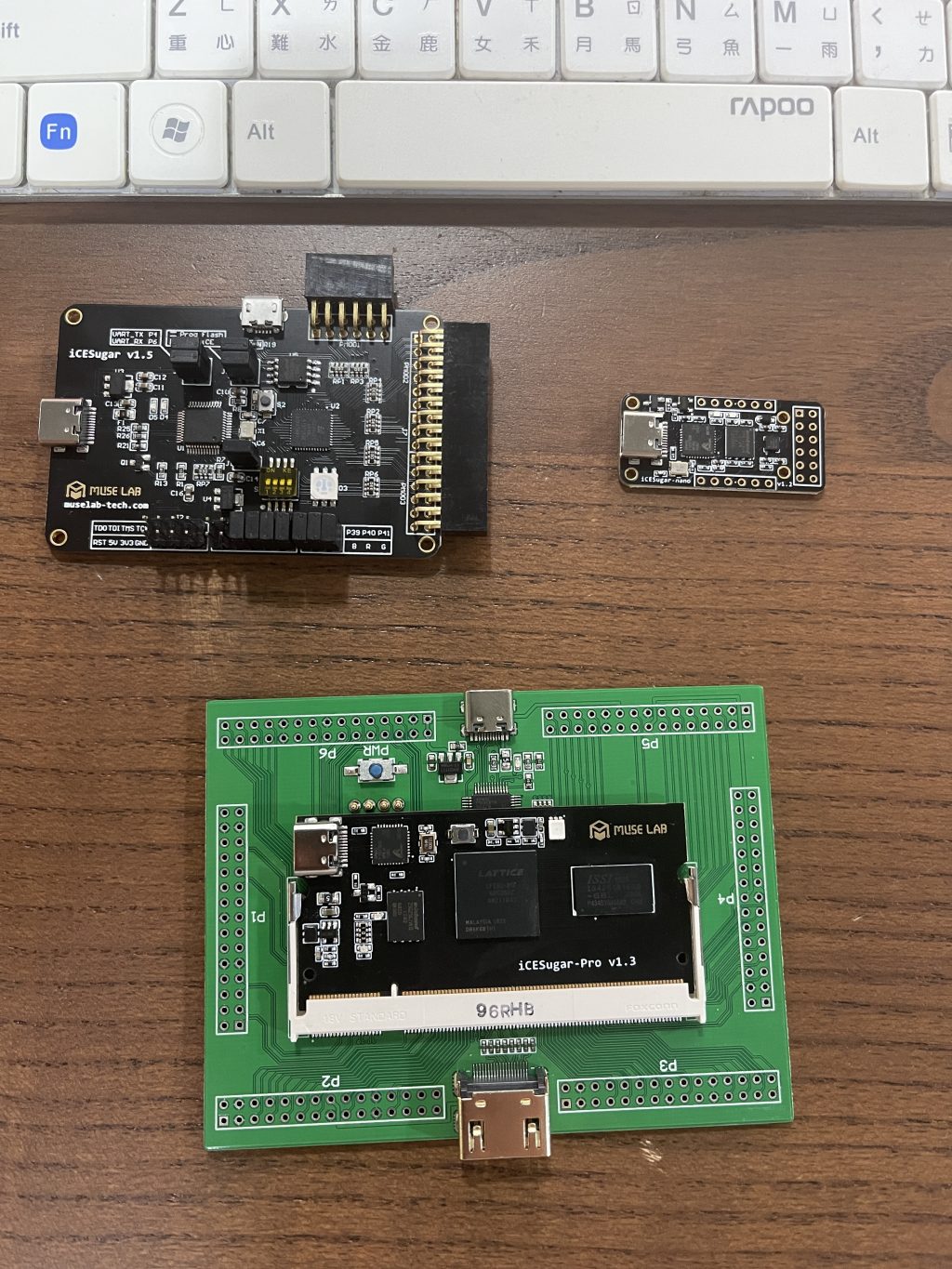

ICESugar board unable to mount in ubuntu

If you unable to mount your icesugar board in ubuntu and saying this error "Not authorized to perform operation", this link resolve it https://benjaminnl.pixnet.net/blog/post/4894925-ubuntu-%E8%A7%A3%E6%B1%BA%E9%9A%A8%E8%BA%AB%E7%A2%9F%E7%84%A1%E6%B3%95%E9%96%8B%E5%95%9F%EF%BC%9Anot-authorized-to-perfo The below board https://item.taobao.com/item.htm?_u=fbuhab0c863&id=631164799875 only work with the extension board on right hand side, the left hand side one dont. I found out the chip in the middle is different, rhs […] 2022/12/15

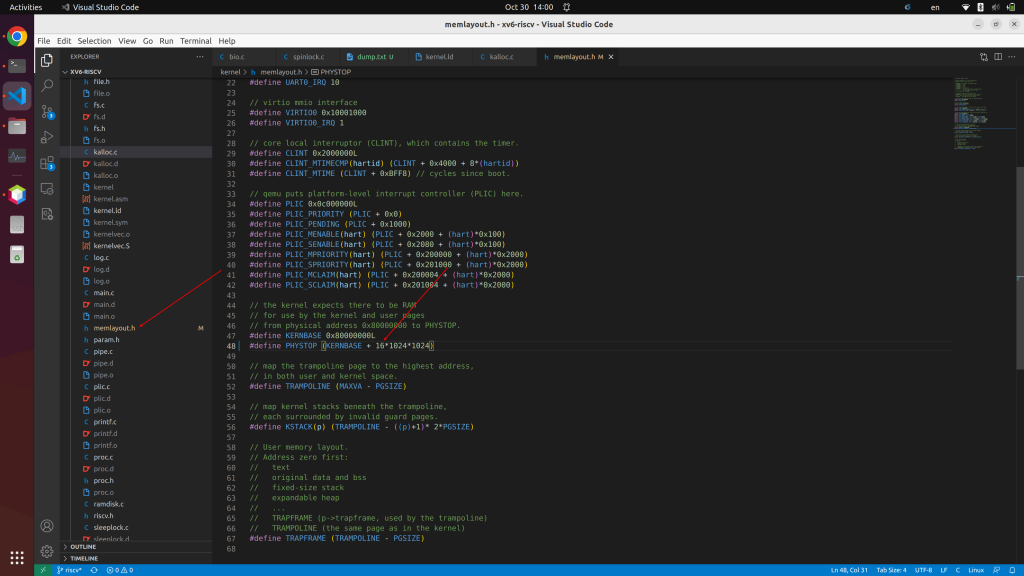

Change qemu to use 16M ram for xv6-riscv

After testing, the minimal memory of xv6-riscv needed is 3MB 2022/10/30

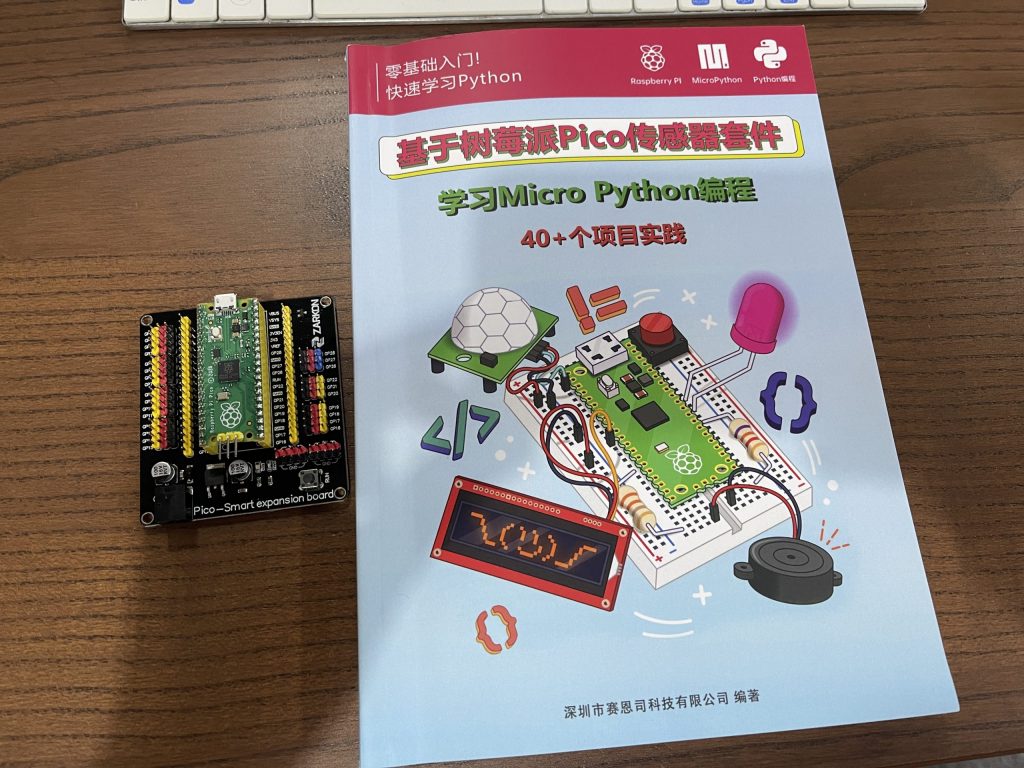

Very good micro python board

https://item.taobao.com/item.htm?spm=a1z09.2.0.0.15412e8duBDI2J&id=645704746945&_u=mbuhab0da05 2022/08/22

Tiny STM32 board (STM32F103C8T6)

https://item.taobao.com/item.htm?spm=a1z09.2.0.0.67002e8ddznHy0&id=630403001847&_u=gbuhab04cbb STM32F103C8T6 2022/08/16

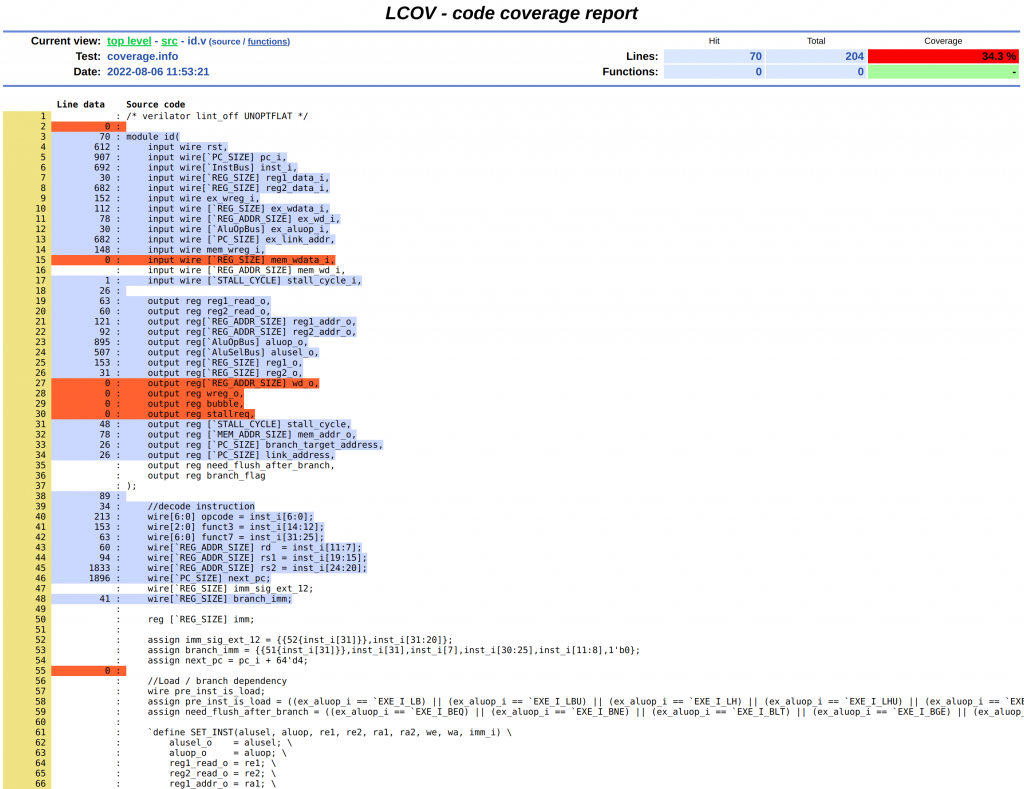

Generate verilator coverage report in html

Remark: https://aijishu.com/a/1060000000330400 brew install iconv or apt-get install lcov 2022/08/06

好書推介

作者用第一身Manager嘅身份教你點謀劃一個ASIC項目 2022/07/17

Clean Architecture

1. 一棟大廈不可能分成兩棟能完全獨立運作的大廈,但軟件通常由能獨立運作的小軟件所組成,所以有理由相信軟件工程比土木工程複雜 2. 軟件工程是內循環的,意思是用軟件A創造軟件B,之後又用軟件B改進軟件A,而土木工程是單向的,所以有理由相信軟件工程比土木工程複雜 3. 就算摩天大廈,起第一層和起第一百層的技術差不多,但軟件中不同層數的建築方法是完全不同,例如os層和web層,所以有理由相信軟件工程比土木工程複雜 4. 軟件工程中做同一件事的方法比土木工程多很多,所以有理由相信軟件工程比土木工程複雜 2022/06/26

Resolved ICESugar pro blink.v :

ERROR: Module rst_gen contains processes, which are not supported by JSON backend (run `proc` first). Edit Makefile $(TARGET).json: $(OBJS) # yosys -p "synth_ecp5 -json $@" $(OBJS) yosys -p "read_verilog -sv $<" -p "synth_ecp5 -json $@" $(OBJS) 2022/03/27

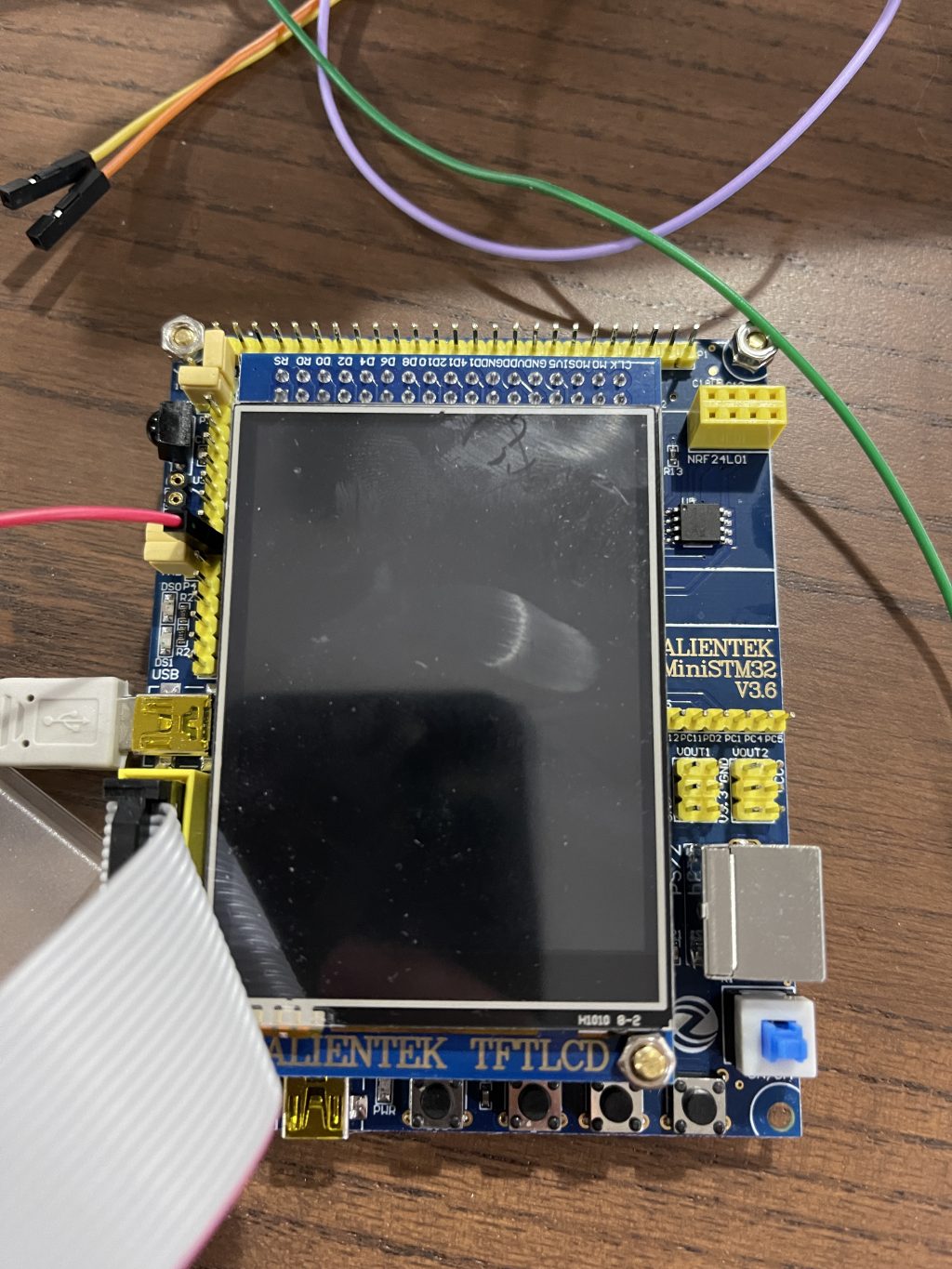

正点原子Mini STM32F103RCT6在STM32CubeMX中玩UART

正點原子的教程是在Keil, 如果要在STM32CubeMX裏玩UART可跟以下步驟 Step 1. Step 2. Comment the whole file Step 3. Add these 3 files from the CD Step 4. Modify usart.c , default example override fputc never works, we have to overrid _write Step 5. Add this 2022/03/25

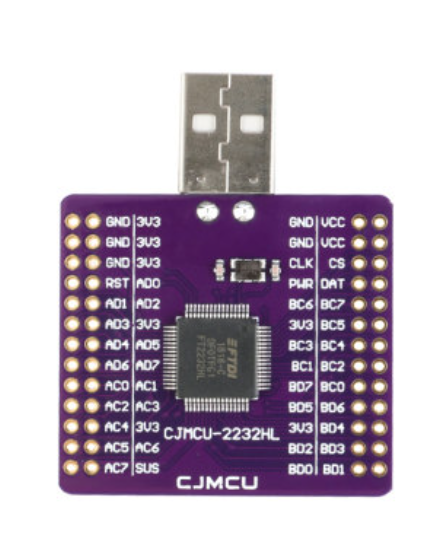

Python read/write jtag via FTDI chip

Bought from here . Example is here https://ftdichip.com/wp-content/uploads/2020/08/AN_110_Programmers_Guide_for_High_Speed_FTCJTAG_DLL-1.pdf Read PWM Pins reference : https://ftdichip.com/wp-content/uploads/2020/07/AN_184-FTDI-Device-Input-Output-Pin-States.pdf 2022/03/03

ICESugarPro board blinking example work

2022/02/27

Arduino Uno programme ATTiny85 works

following https://jimirobot.tw/arduino-tutorial-attiny-attiny85-uno-burn/ 2022/02/20

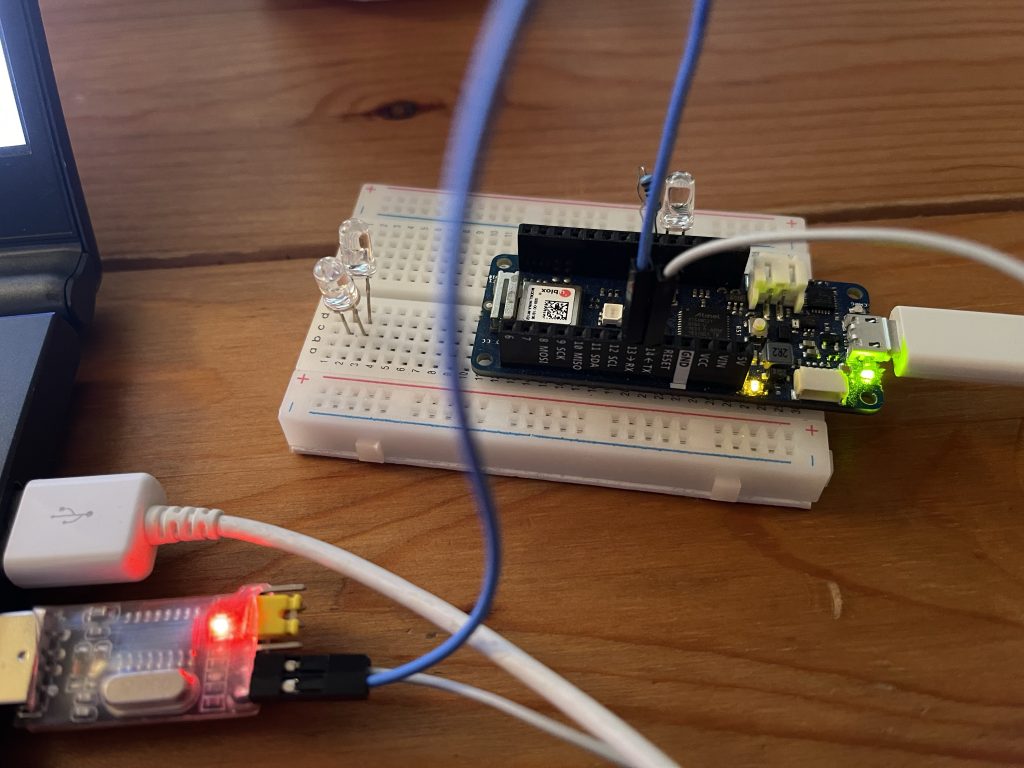

MRK Wifi 1010 serial is different

Arduino MRK Wifi 1010 serial is different than Nano and Uno, the usb-to-serial and in D13/14 are separate, so code them this way 2022/02/20

start point to build our own jtag for our risc-v cpu

After days of hacking, i finally found out there is a dummy driver in openocd. just ./configure --enable-dummy and run it by ./bin/openocd -c 'interface dummy' -c 'adapter_khz 1' , you can see the dummy driver is running and in the function "static int dummy_write(int tck, int tms, int tdi)", we can manually toggle the […] 2022/02/13

Compile libsigrok and pulseview in windows by msys2

This is the tutorial to build libsigrok and pulseview in windows Download msys https://www.msys2.org/ Open "MSYS2 MinGW x64", don't use "MSYS2 MSYS" 3. git clone https://github.com/sigrokproject/sigrok-util.git 4. cd sigrok-utils/cross-compile/msys2 5. ./sigrok-native-msys2 prepare , it will auto install all necessary packages Compile libsigrok 6. git clone https://gitlab.com/quantr/toolchain/libsigrok.git 7. cd libsigrok 8. ./autogen.sh 9. vi configure and […] 2022/02/06

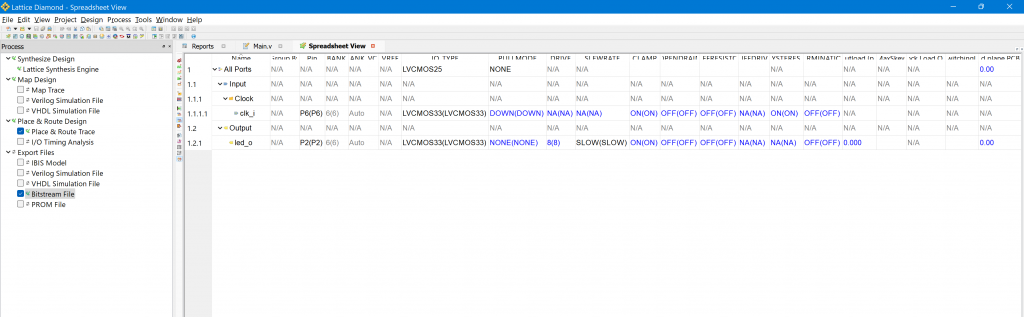

CPU ex.v progress 2022/01/10

2022/01/10

Openlane + wsl2 : repository does not exist or may require 'docker login'

when you have this problem 2022/01/01

Openlane init files

If run fail, have to remove the "runs" folder before rerun, otherwise same error will be shown initProject.sh runProject.sh my_design.v config.tcl 2021/12/31

Arithmetic Circuits & Multipliers

https://web.mit.edu/6.111/www/f2016/handouts/L08_4.pdf 2021/12/12

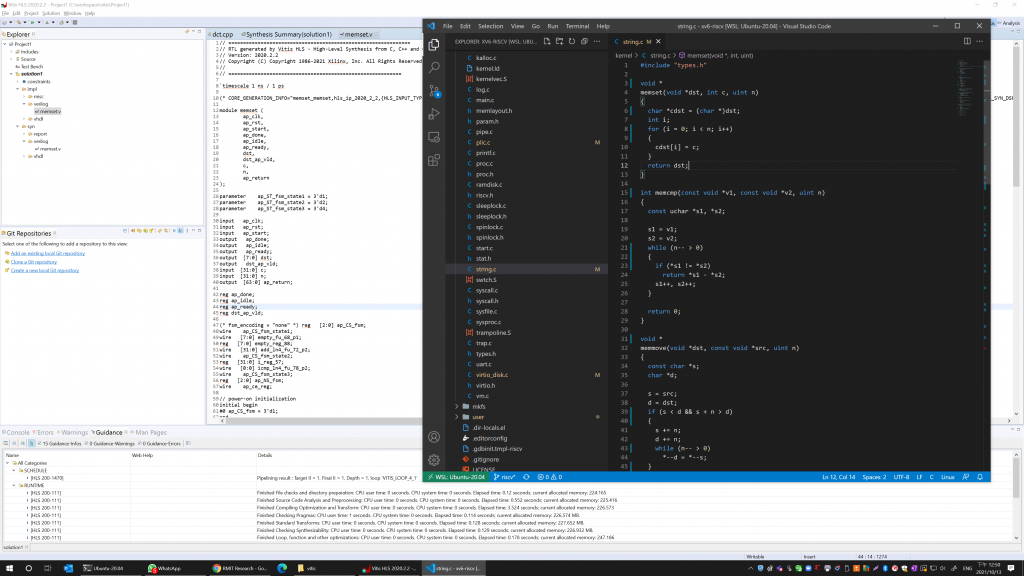

HLS

Synthesis-ed part of XV6 into Verilog 2021/10/13

Good web to learn RISC-V interrupt

https://github-wiki-see.page/m/ianchen0119/AwesomeCS/wiki/Hello%2C-OS%21 https://github-wiki-see.page/m/ianchen0119/AwesomeCS/wiki/2-5-RISC-V::%E4%B8%AD%E6%96%B7%E8%88%87%E7%95%B0%E5%B8%B8%E8%99%95%E7%90%86----PLIC-%E4%BB%8B%E7%B4%B9 https://github-wiki-see.page/m/ianchen0119/AwesomeCS/wiki/2-4-RISC-V::%E4%B8%AD%E6%96%B7%E8%88%87%E7%95%B0%E5%B8%B8%E8%99%95%E7%90%86----%E4%B8%AD%E6%96%B7%E7%AF%87 2021/08/29

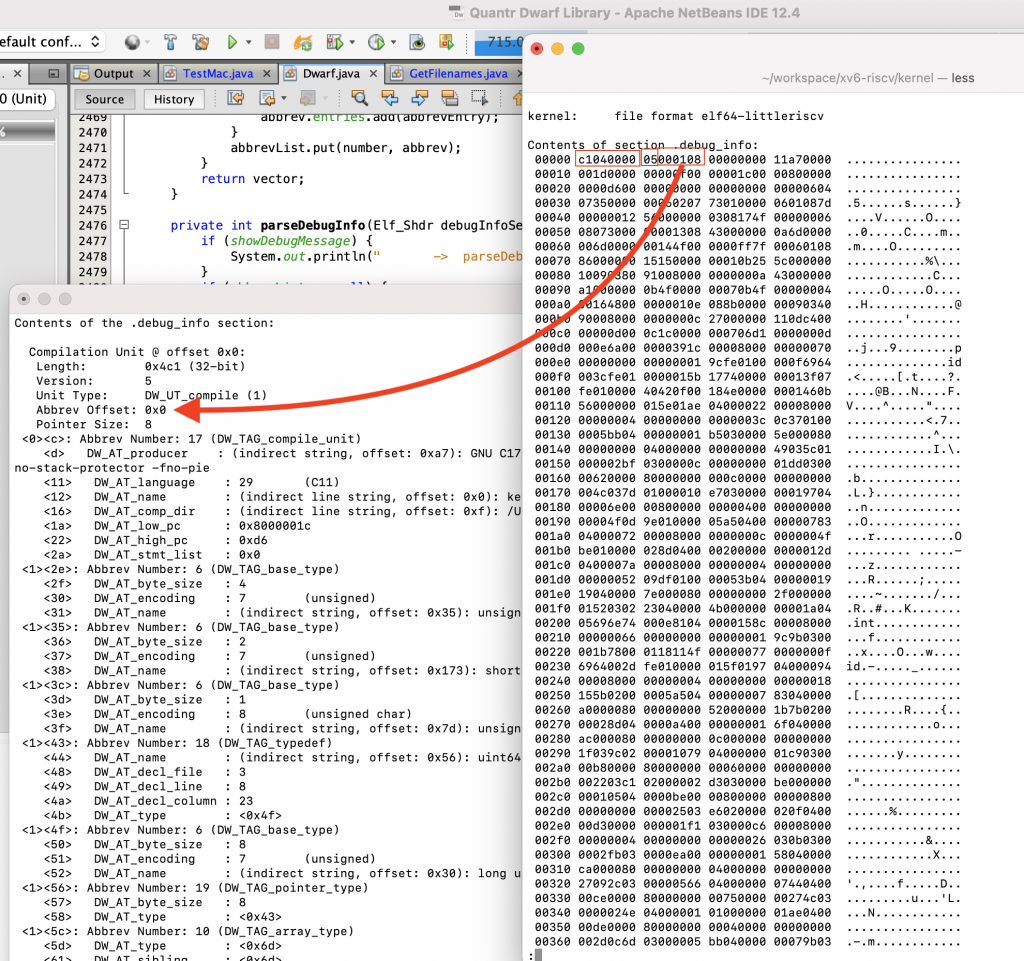

RISC-V readelf may has bug on field Abbrev Offset

2021/08/05

Good electronic components book

2021/05/30

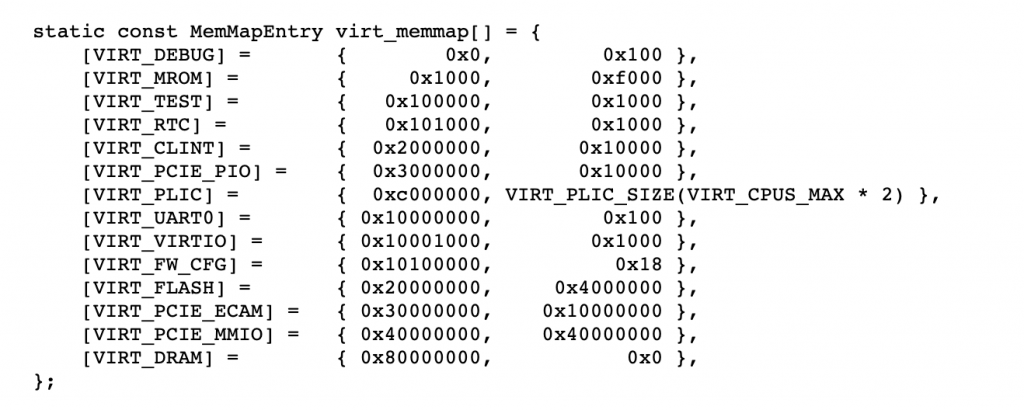

RISC-V Qemu memory mapping

https://github.com/qemu/qemu/blob/master/hw/riscv/virt.c 2021/05/11

Minimial Arduino with ATTiny85

2021/04/17

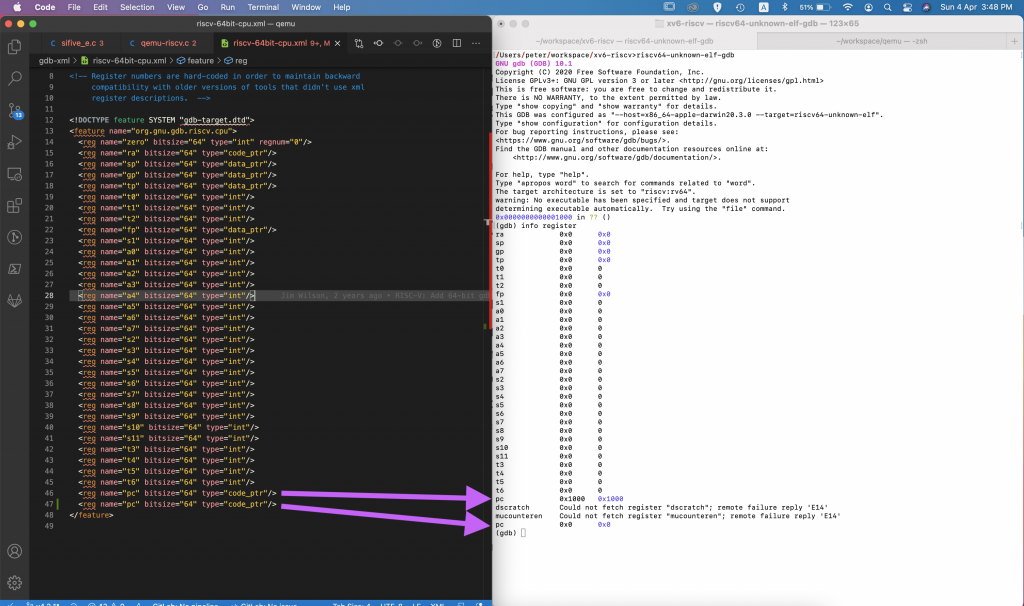

This file controls how "info register" in gdb

this file riscv-64bit-cpu.xml controls how "info register" printing values in gdb. I tried to add one entry to it to print the "PC" value one more time, it works 2021/04/04