Category Archives: Computer Engineering

XV6 book March 22, 2021

2021/03/22

RISC-V progress

挾左個vscode web版落我地個web到,開發埋自己個theme親返隻色。RISC-V asm個syntax highlight仲差少少。跟住就可以放俾澳洲啲大學生上黎係web到做RISC-V coding,simulator我部server應該頂到200-500人。 2021/03/08

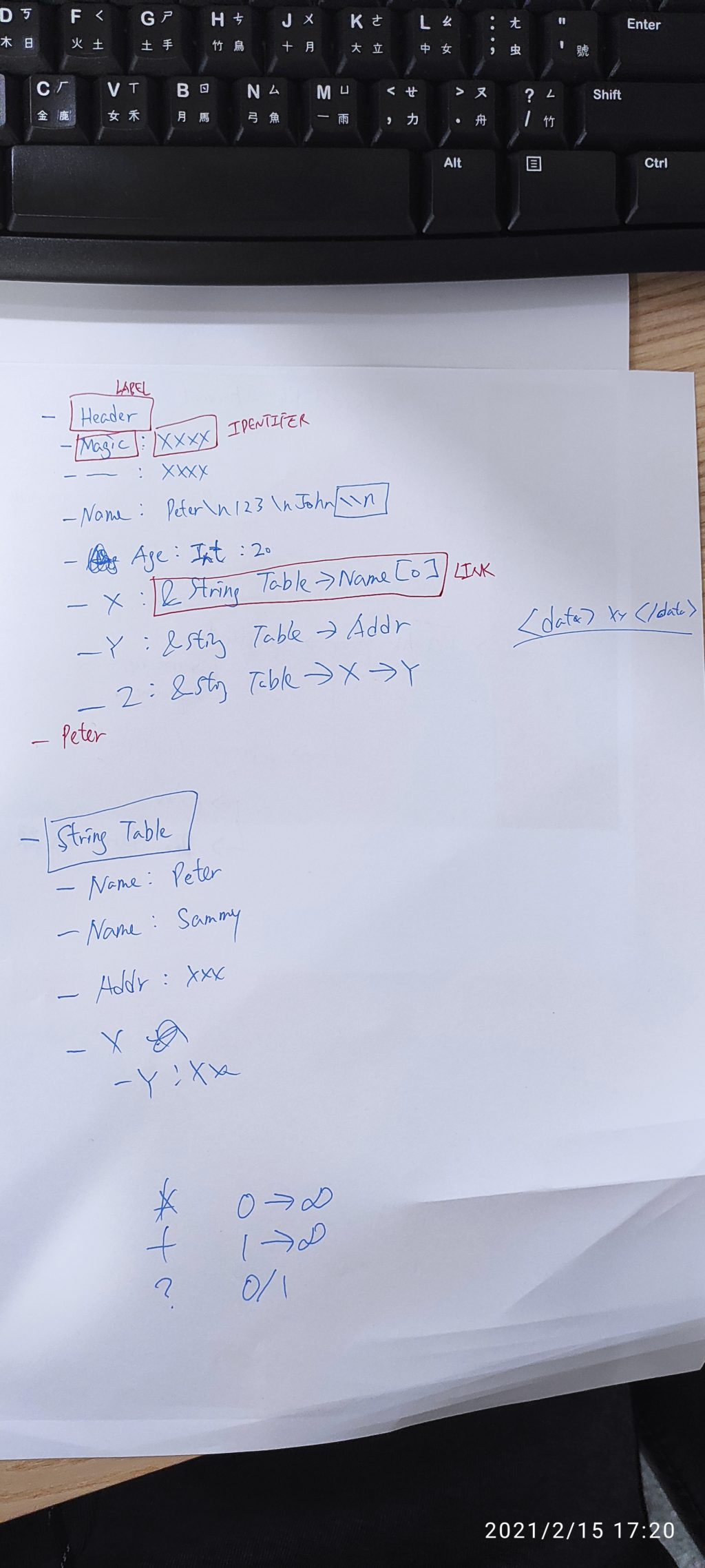

HK Data format - draft one

2021/03/07

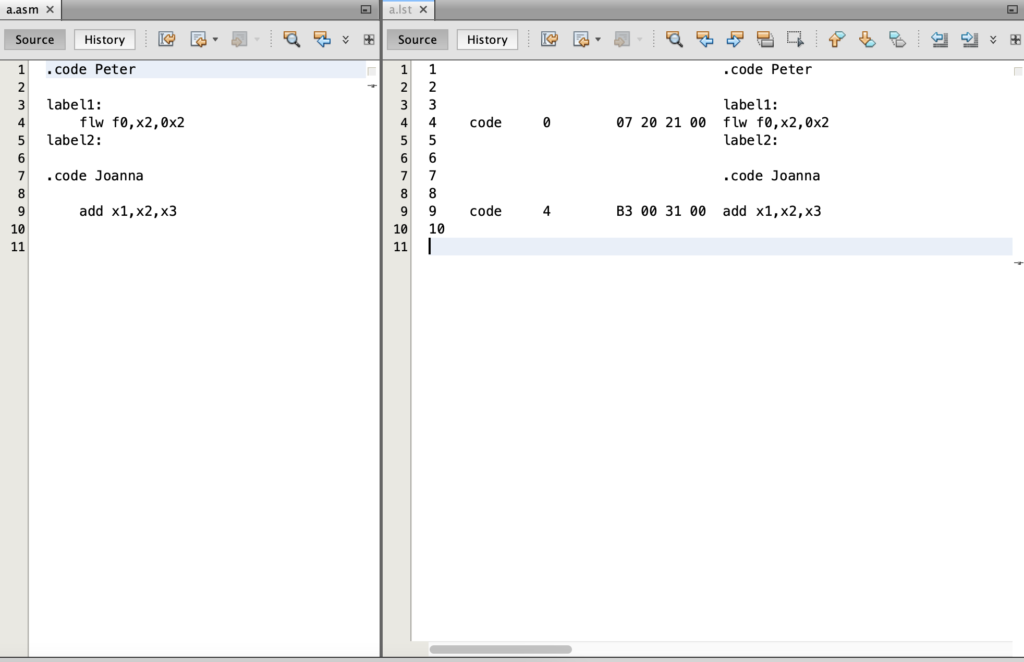

Assembler listing is done

2021/03/05

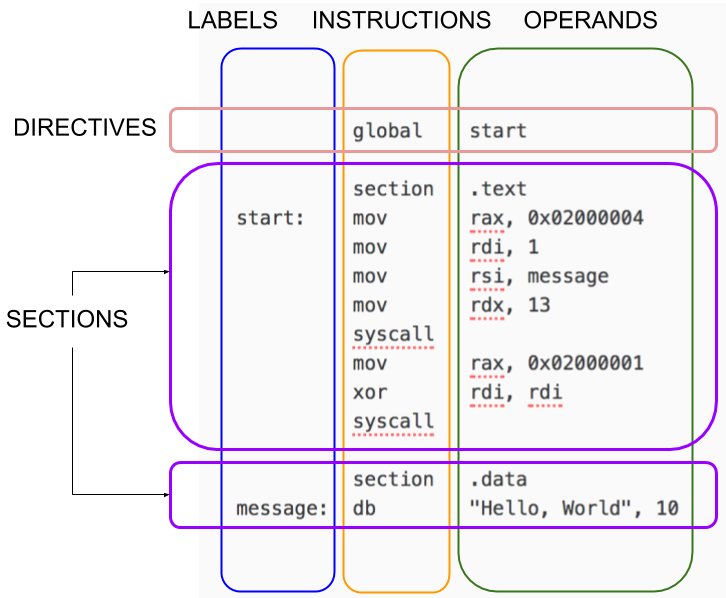

Structure of a NASM Program

2021/02/14

Tutorial to use Hantek6022BE with Pulse

Step 1. Download pulseview Step 2. Make sure this button is poped out. Step 3. Install Zadig driver Step 4. Run pulseview, the device should be auto detected as "Saleae Logic", but not "Hantek", anyway it will works 2021/02/13

INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986

INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986 2021/02/05

RISC-V CPU verilog testbench is good now

2021/01/31

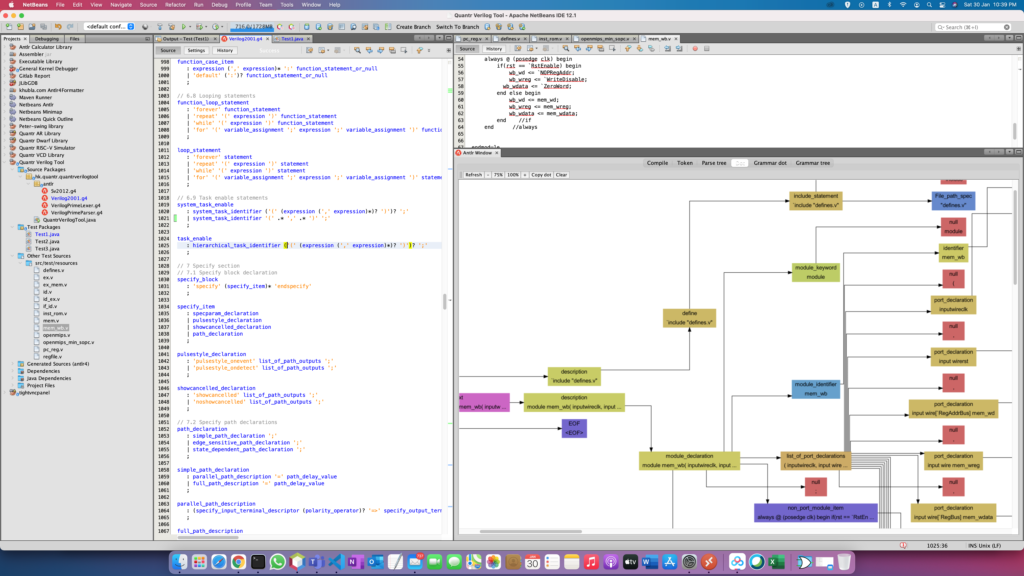

Antlr parses verilog

Default antlr's verilog grammar can't parse verilog right, i modified a little bit to make it parse my verilog files. Here is the modified grammar https://gitlab.com/quantr/toolchain/quantr-verilog-tool/-/blob/master/src/main/java/hk/quantr/quantrverilogtool/antlr/Verilog2001.g4 2021/01/30

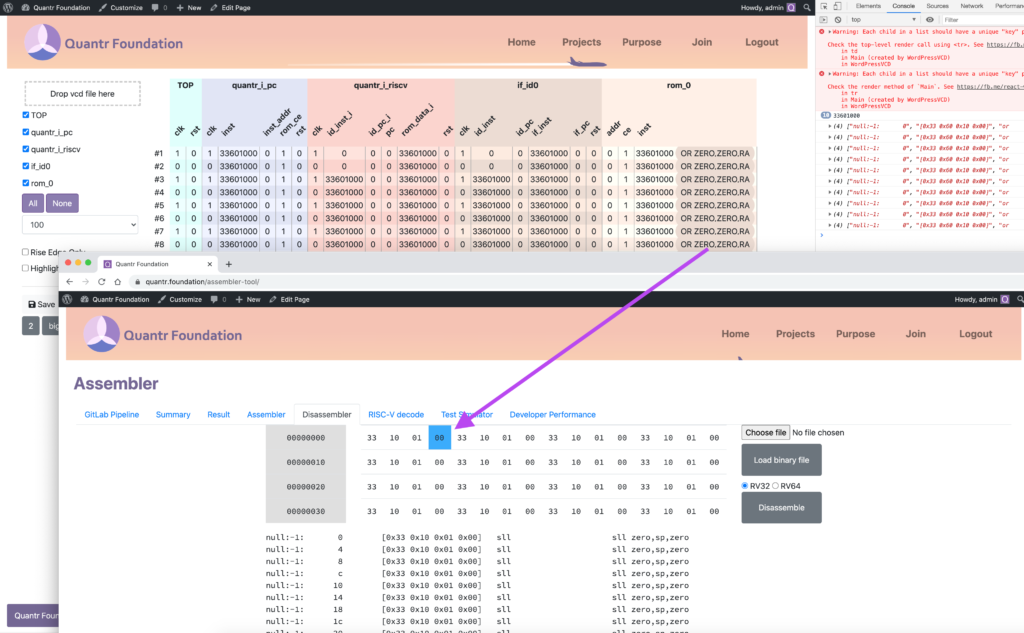

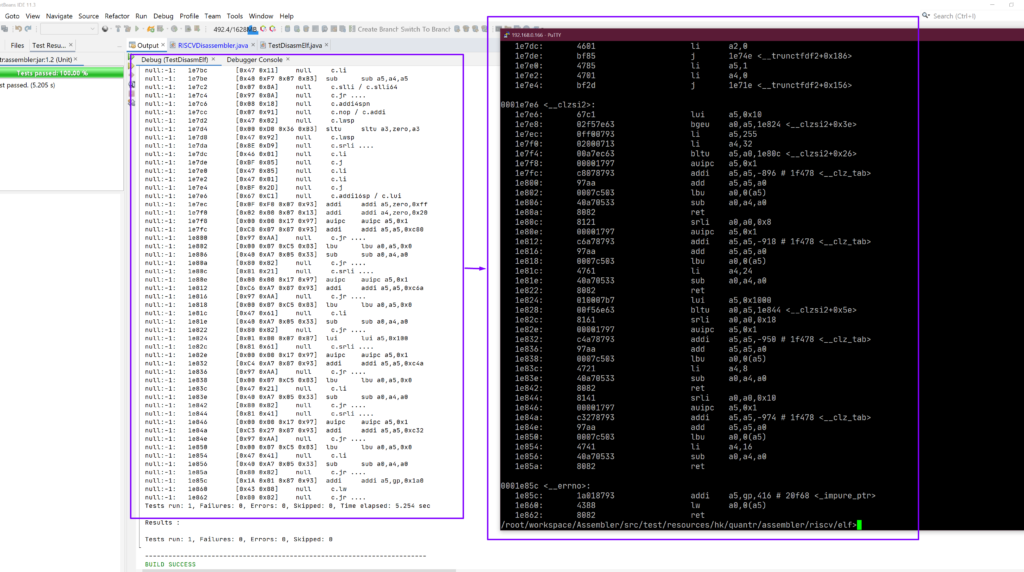

CPU testbench同assembler testbench而家link埋

它可以幫手check下cpu decode有無錯了 2021/01/15

RISC-V 64 bits XV kernel insturctions

addaddiaddiwaddwamoadd.damoadd.wamoadd.w.rlamoswap.wamoswap.w.aqandandiauipcbeqbeqzbgebgeubgezbgtzblezbltbltubltzbnebnezc.addc.lic.luic.mvc.nopc.sllic.slli64c.srai64csrccsrcic.srli64csrrcsrrccsrrcicsrrscsrrsicsrrwcsrrwicsrscsrwdivuwebreakecallfadd.qfadd.sfdiv.dfdiv.sfencefldflqflwfmadd.dfmadd.sfmsub.dfmsub.qfmsub.sfnmadd.dfnmadd.qfnmadd.sfnmsub.dfnmsub.qfnmsub.sformatfsdfswjjaljalrjrlblbuldlhlhuliluilwlwumretmulmulwmvnegnegwnopnotororiremuwretsbsdsectionseqzsext.wsfence.vmashsllsllislliwsllwsltsltisltiusltusltzsnezsraisraiwsretsrlsrlisrliwsrlwsubsubwswunimpxorxori 2020/12/31

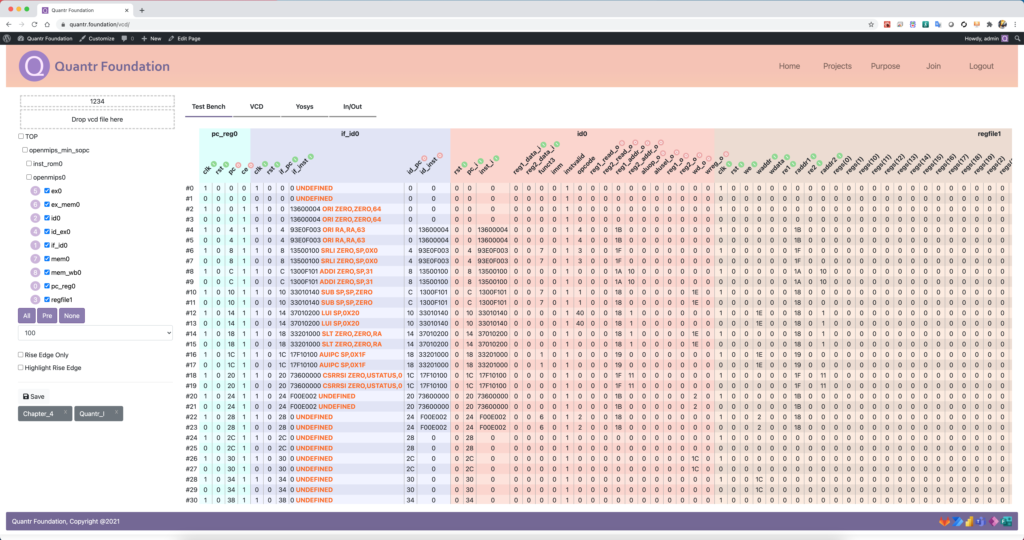

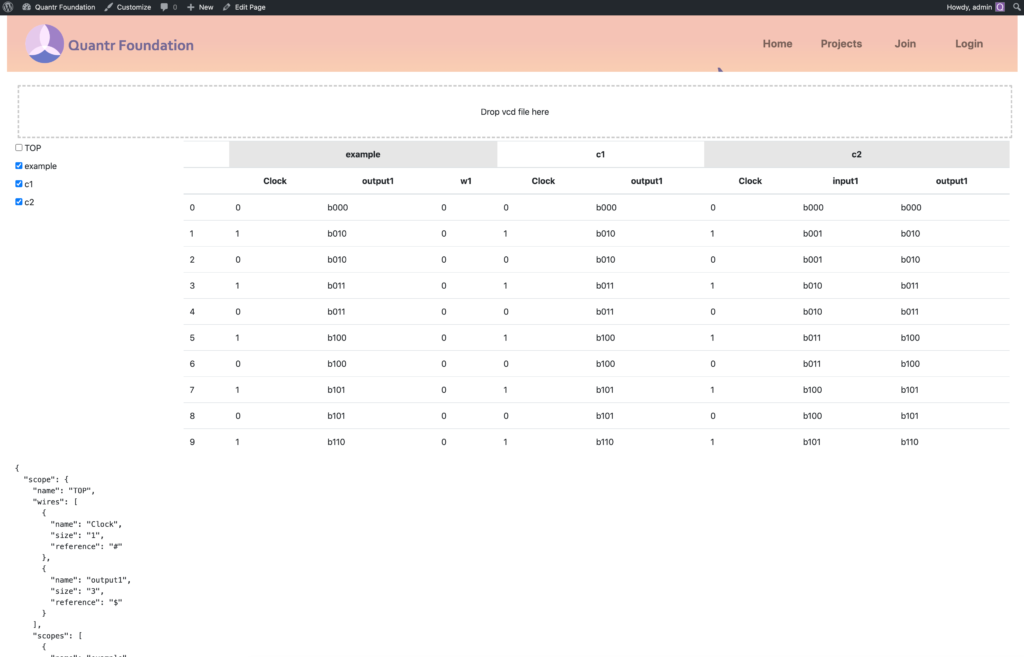

self-made tool for risc-v development

Another self-made tool for risc-v development, it is a vcd file dumper. With our own dumper, we can record the behavior of another risc-v, so we can cross check our risc-v correctless much more efficient. 2020/12/29

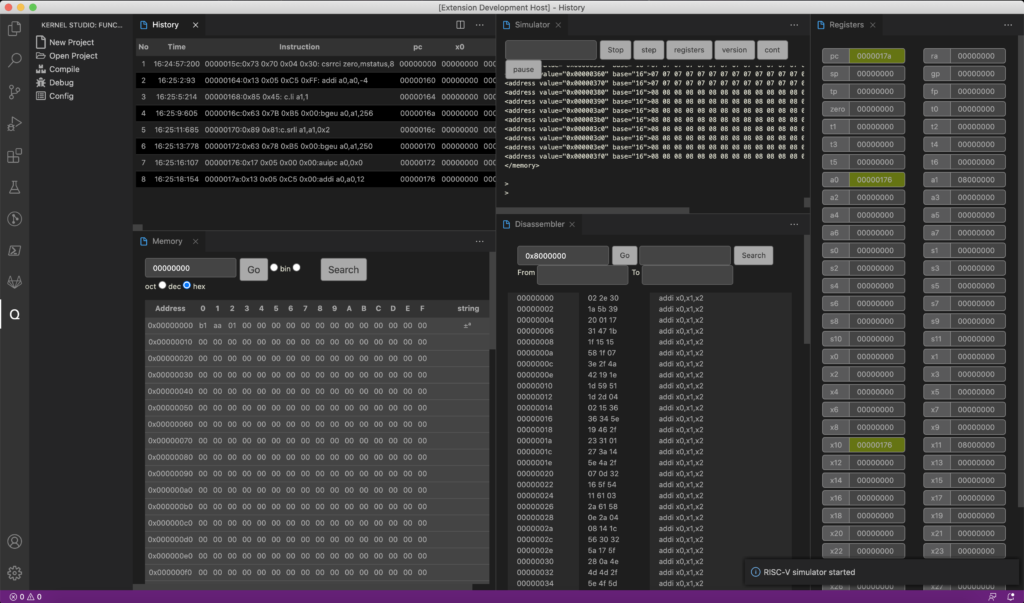

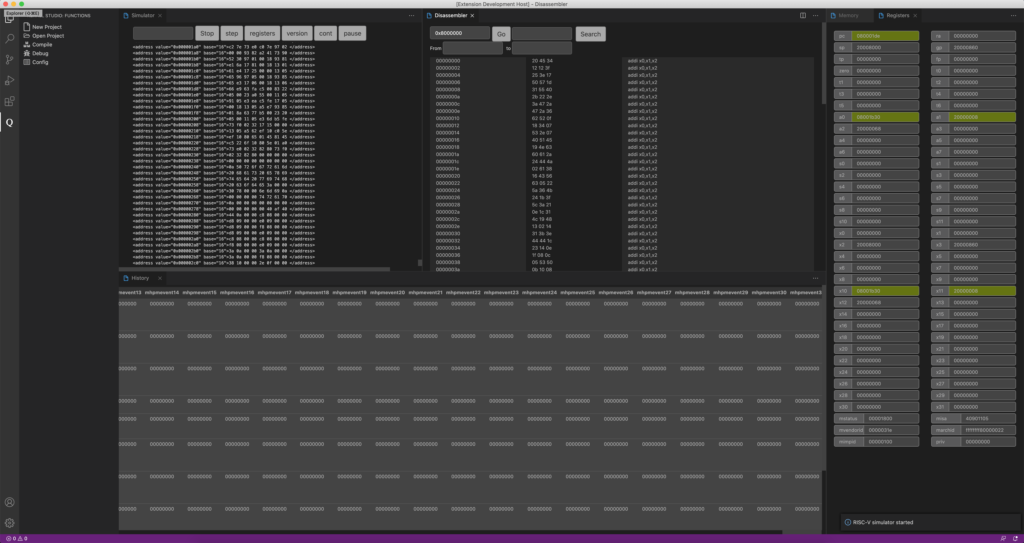

Kernel Studio dev progress

2020/11/12

Running 64- and 32-bit RISC-V Linux on QEMU

https://risc-v-getting-started-guide.readthedocs.io/en/latest/linux-qemu.html Running 64- and 32-bit RISC-V Linux on QEMU This is a “hello world” example of booting Linux on RISC-V QEMU. This guide covers some basic steps to get Linux running on RISC-V. It is recomended that if you are interested in a specific distrubution you follow their steps. For example if you are interested […] 2020/11/10

XF6 kernel use these instructions

2020/11/10

Our RISC-V simulator interface

2020/10/29

GD32 RISC-V registers

===== RISC-V Registers(0) zero (/32)(1) ra (/32)(2) sp (/32)(3) gp (/32)(4) tp (/32)(5) t0 (/32)(6) t1 (/32)(7) t2 (/32)(8) fp (/32)(9) s1 (/32)(10) a0 (/32)(11) a1 (/32)(12) a2 (/32)(13) a3 (/32)(14) a4 (/32)(15) a5 (/32)(16) a6 (/32)(17) a7 (/32)(18) s2 (/32)(19) s3 (/32)(20) s4 (/32)(21) s5 (/32)(22) s6 (/32)(23) s7 (/32)(24) s8 (/32)(25) s9 (/32)(26) […] 2020/09/06

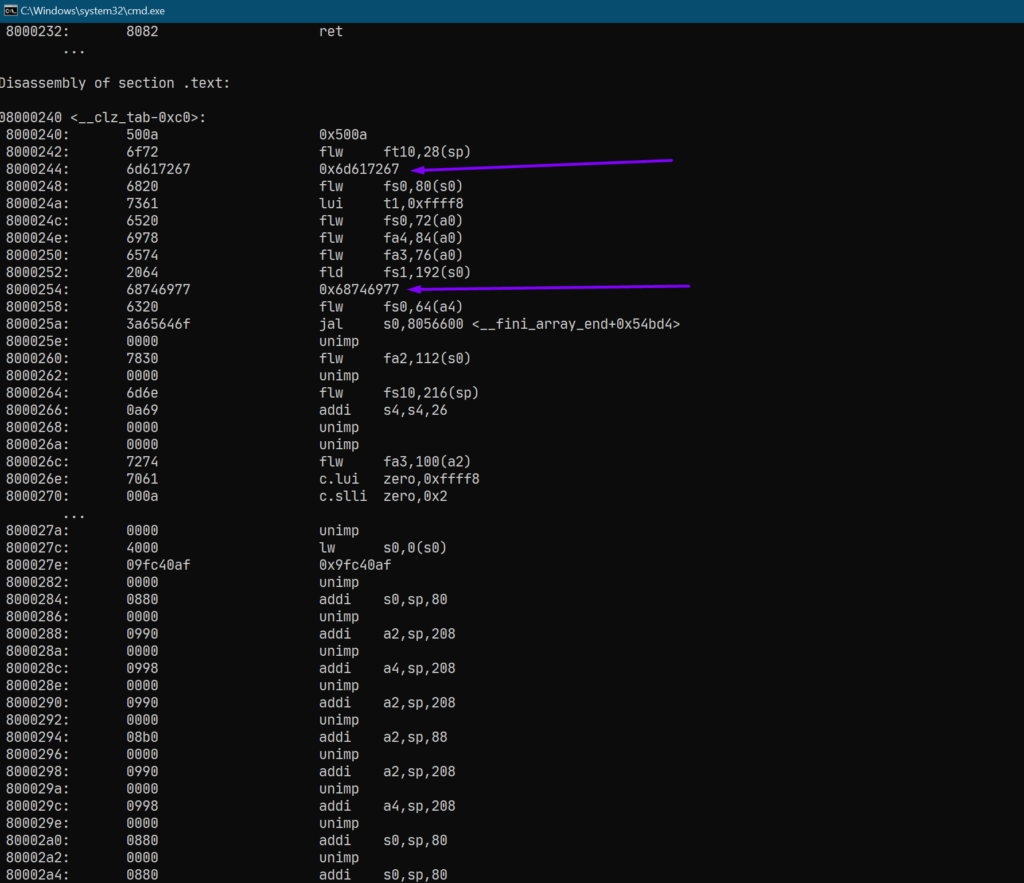

RISC-V objdump disassemble bug

2020/08/28

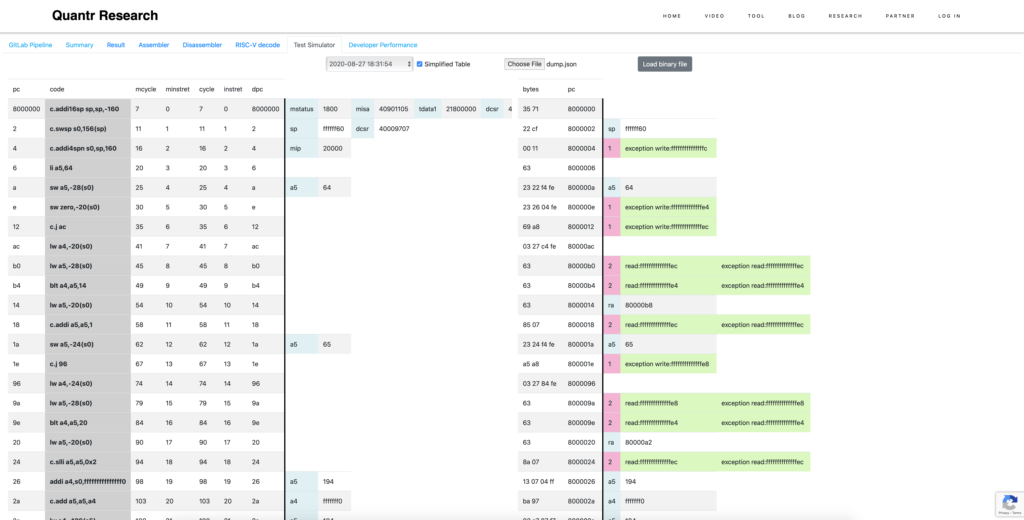

Good progress on RISC-V simulator development

We have good progress, finished running 3 examples successfully. Go jump in to simulate some big examples. 2020/08/27

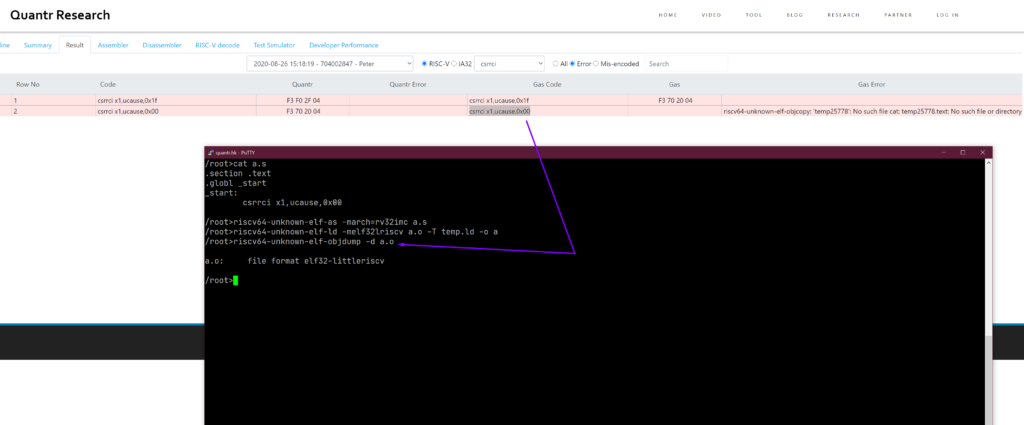

I think RISC-V gas has bug

Compiling instruction "csrrci x1,ucause,0x00" produce no bytes 2020/08/26

RISC-V progress

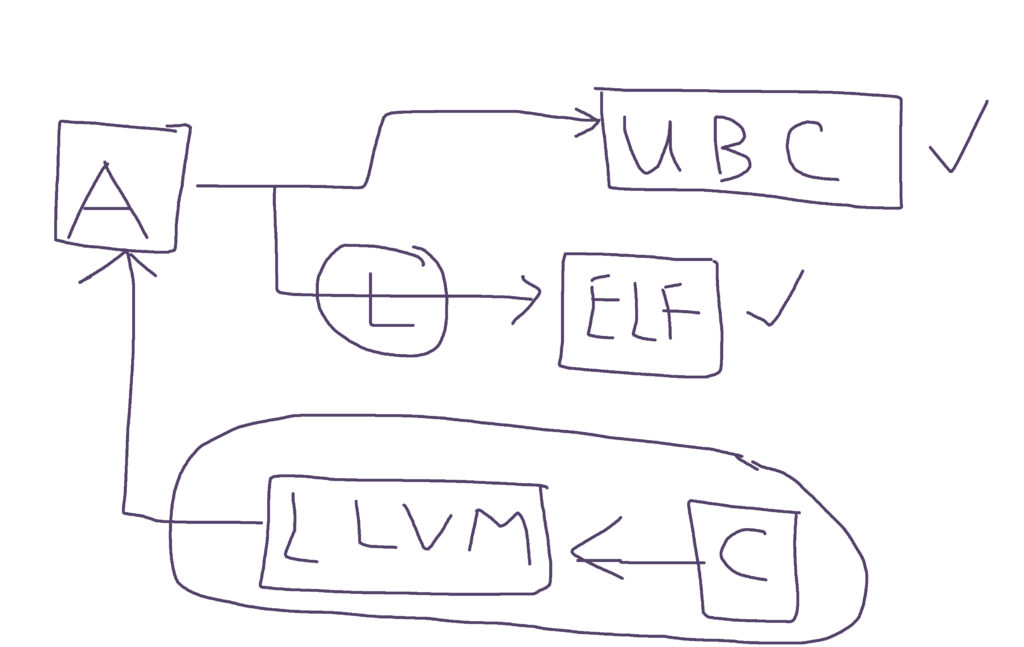

RISC-V encoding part & decoding part of assembler and disassembler for imc are done. 2020/07/20

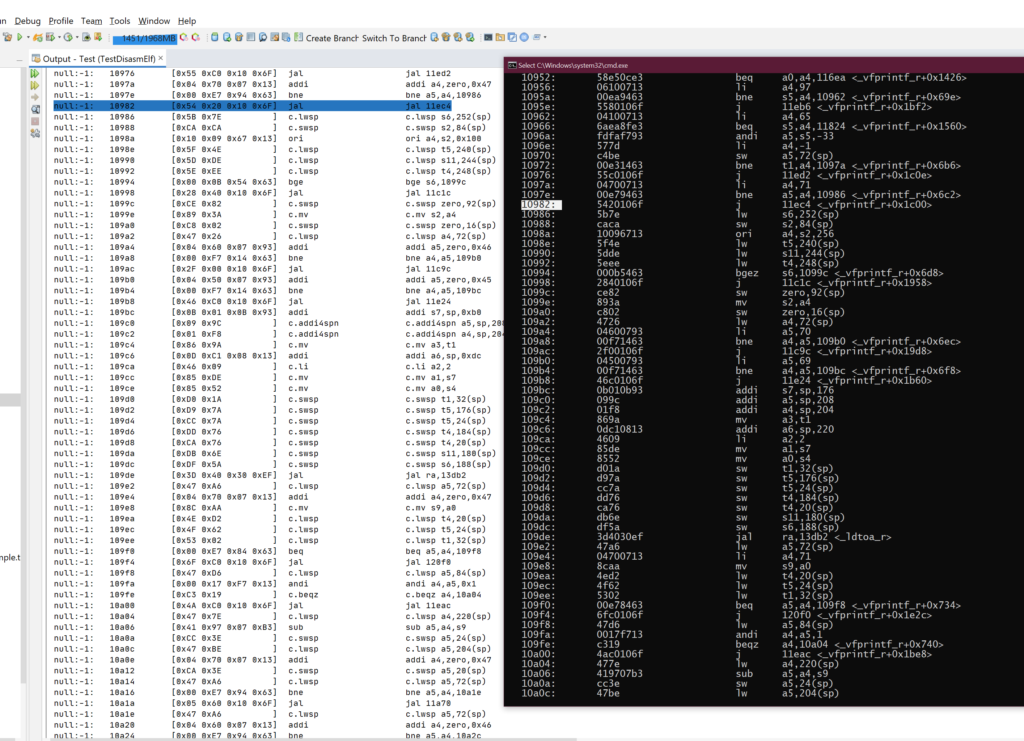

RISC-V disassembler can decode whole RV32IC

I think i can finish the RISC-V disassembler these two weeks. So far it can successfully decode RV32IC and ELF. 2020/07/04

Hour of code 2020/06/27 RISC-V assembly

2020/06/30

riscv green card is wrong

c.sub should be CA format, not CR 2020/06/21

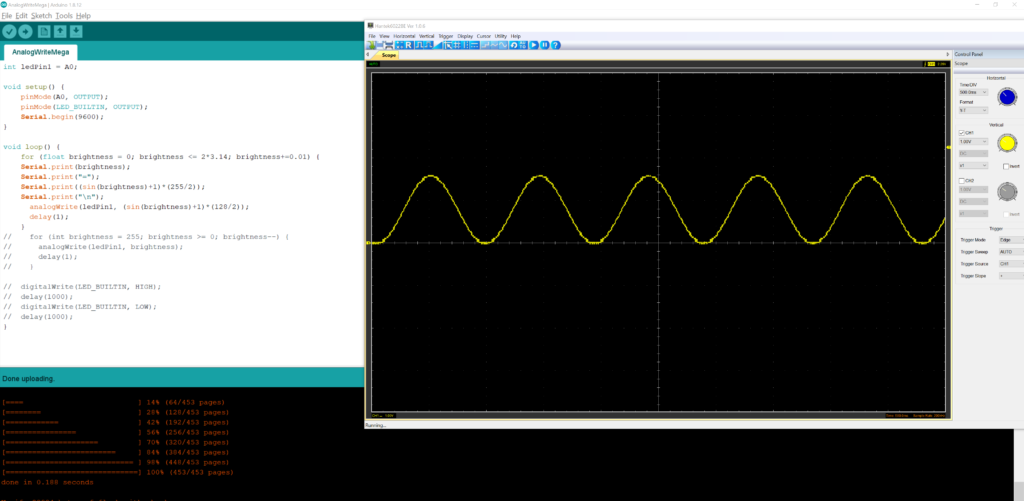

Arduino output sine wave, it works

My Arduino board has built-in DAC, can output sine wave. 2020/06/14

compressed instructions is working in testbench web

2020/06/13

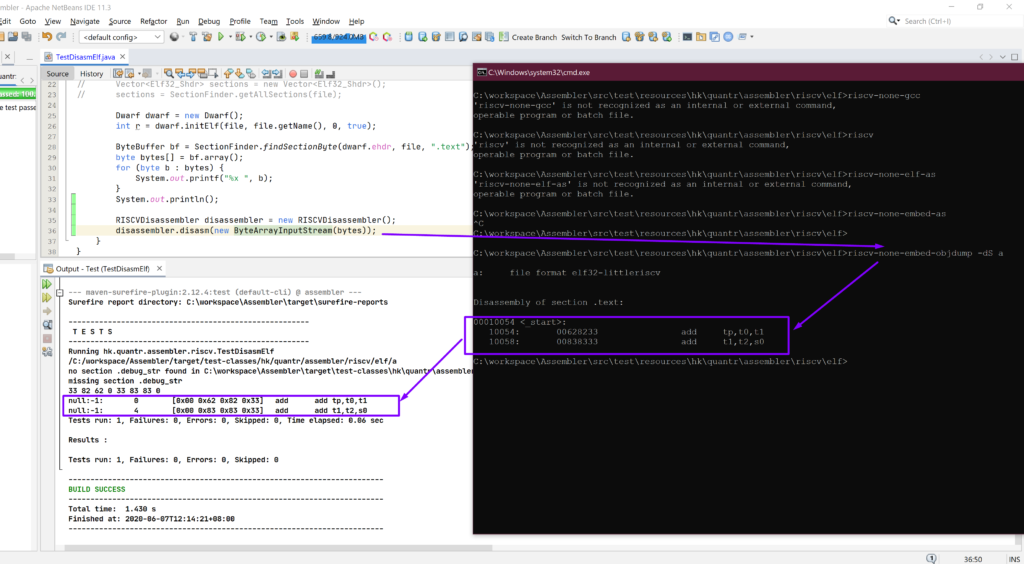

Can disasm RISC-V code from ELF

2020/06/07

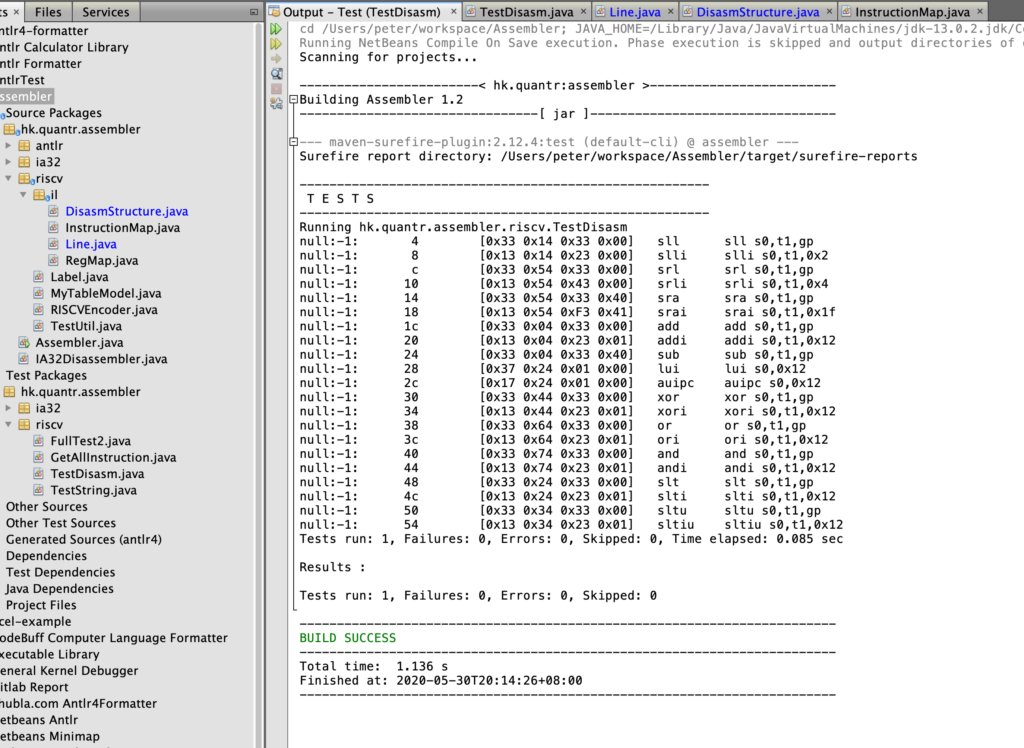

ASSEMBLER MEETUP #42, 2020/05/30

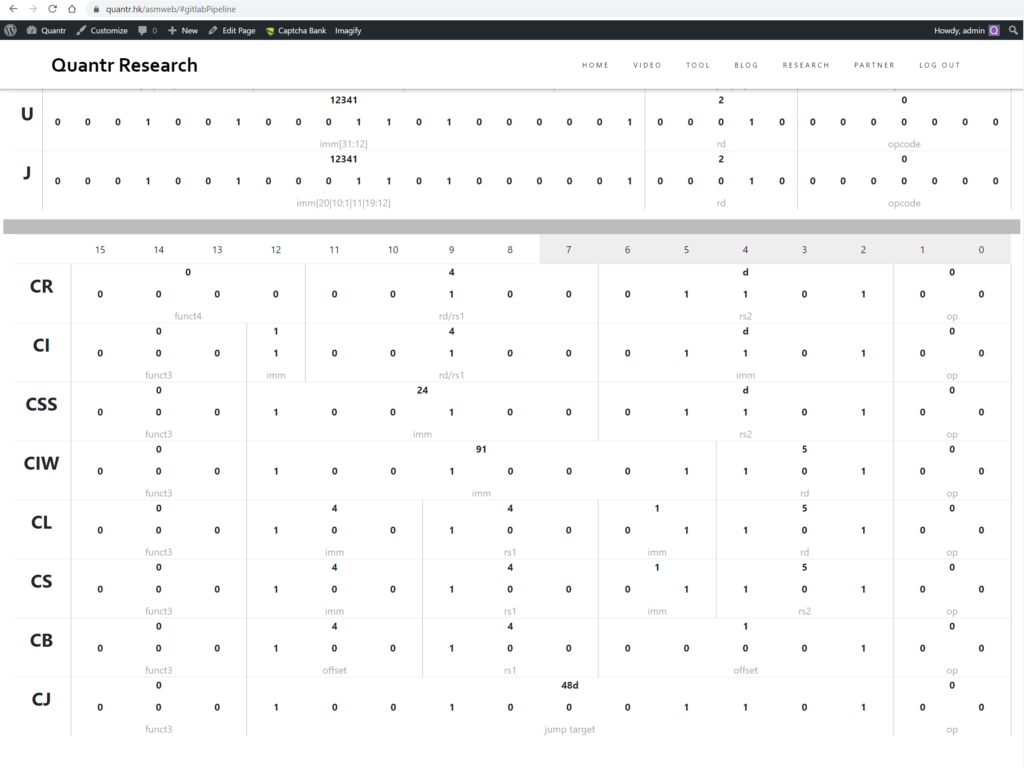

Doing RISC-V assembler, this is our first decode screen 2020/05/30

RISC-V Instruction set naming

2020/05/30

short-term risc-v plan 20200523

2020/05/23

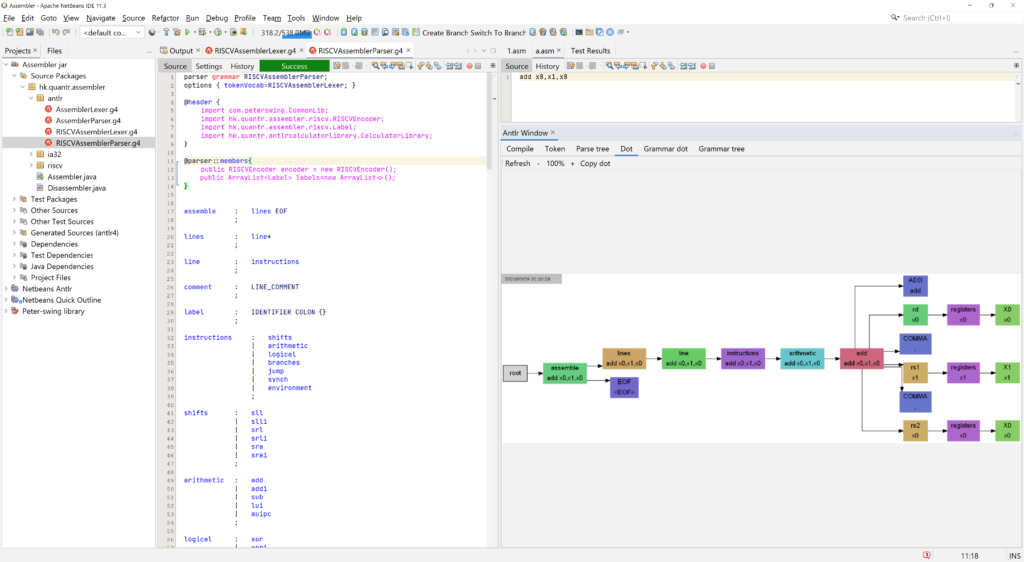

6 hours to fix my antlr netbeans plugin

Used near 6 hours to fix my netbeans-antlr plugin. I have to remember these: Netbeans build in antlr library have to in-sync with the antlr i am using in my pluging. If they in different version, unexpected result will come out. In windows, if antlr grammar has some mistakes (I meant not problems, your grammar […] 2020/05/09

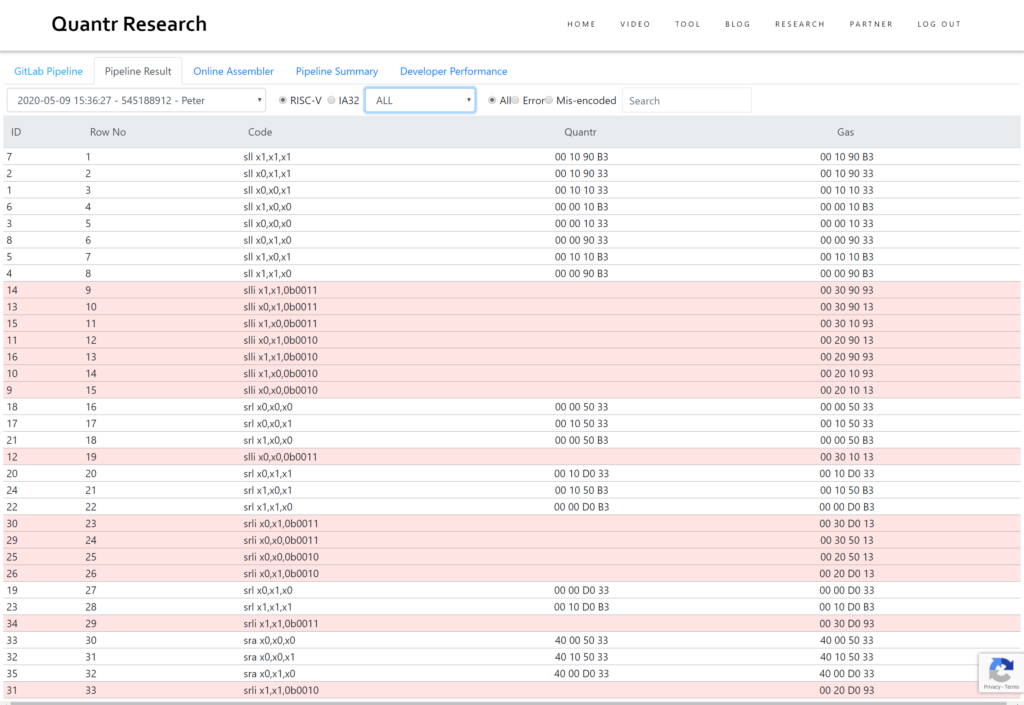

ASSEMBLER MEETUP #41, 2020/05/09

added RISC-V supports to our testbench portal 2020/05/09

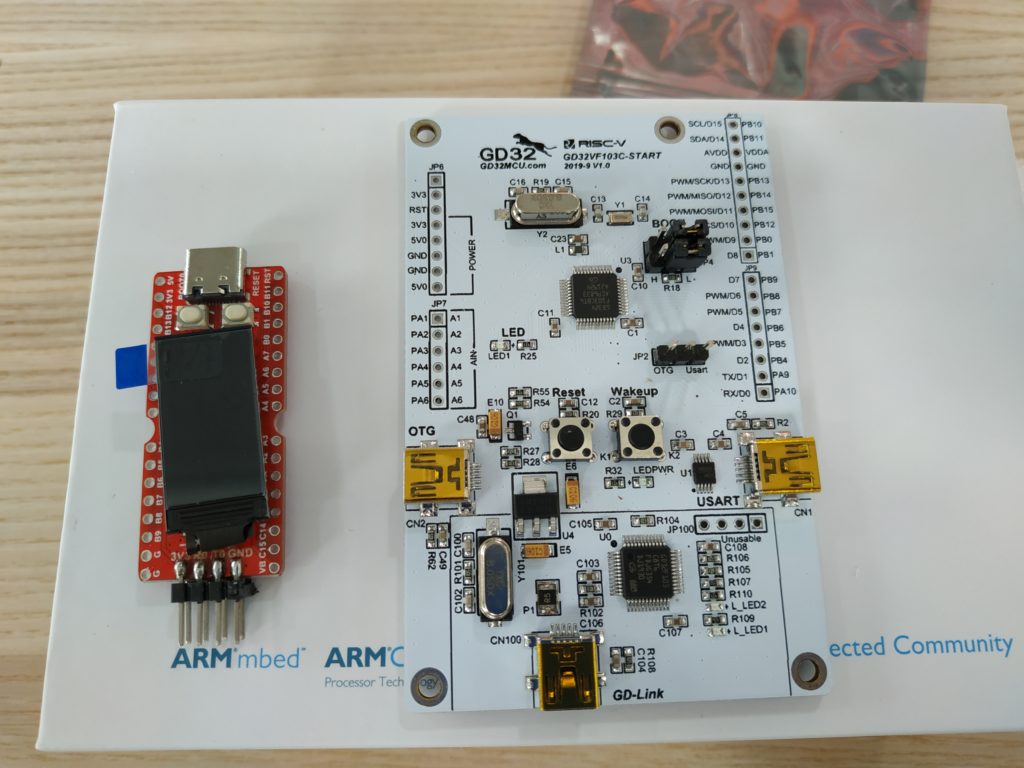

RISC-V boards arrived

Let's do some real experiments on these boards: https://item.taobao.com/item.htm?spm=a230r.1.14.201.65363b3cWNnt8y&id=609421832198&ns=1&abbucket=1#detail https://item.taobao.com/item.htm?spm=a230r.1.14.213.65363b3cWNnt8y&id=606277334580&ns=1&abbucket=1#detail 2020/05/04

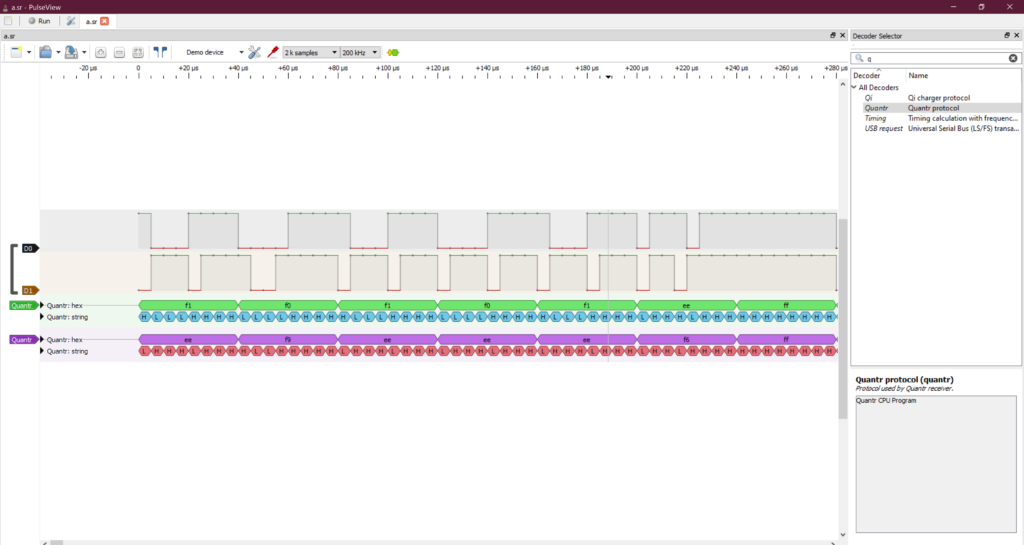

Conquer the Sigrok decoder development

2020/05/03

小組討論一下RISC-V的assembly東西

2020/04/27

ASSEMBLER MEETUP #37, 2020/04/11

We agreed to put x86 and risc-v assembler code into one project, so up one level for the java package, make it ready to stuck in risc-v code I will write the first risc-v assembly grammar and upgrade www.quantr.hk/asmweb to support risc-v test cases Learning vscode extension development, make myself ready to create a debugger […] 2020/04/11

Assembler Meetup #34, 2020/03/21

Only 42 instructons are wrong. We are close to first milestone. Will study "Island Grammar", hope it is the way to embed other antlr grammar from the main one. 2020/03/22

Assembler Meetup #32, 2020/03/07

Still working on the Antlr grammar to supports "Label" Very naive skillset on Antlr, just bouht the english version of this book, re-read it again. Chinese one not very comfortable to read. We think we can complete the first release of the assembler within 3 months. 2020/03/07

Assembler Meetup #30, 2020/02/15

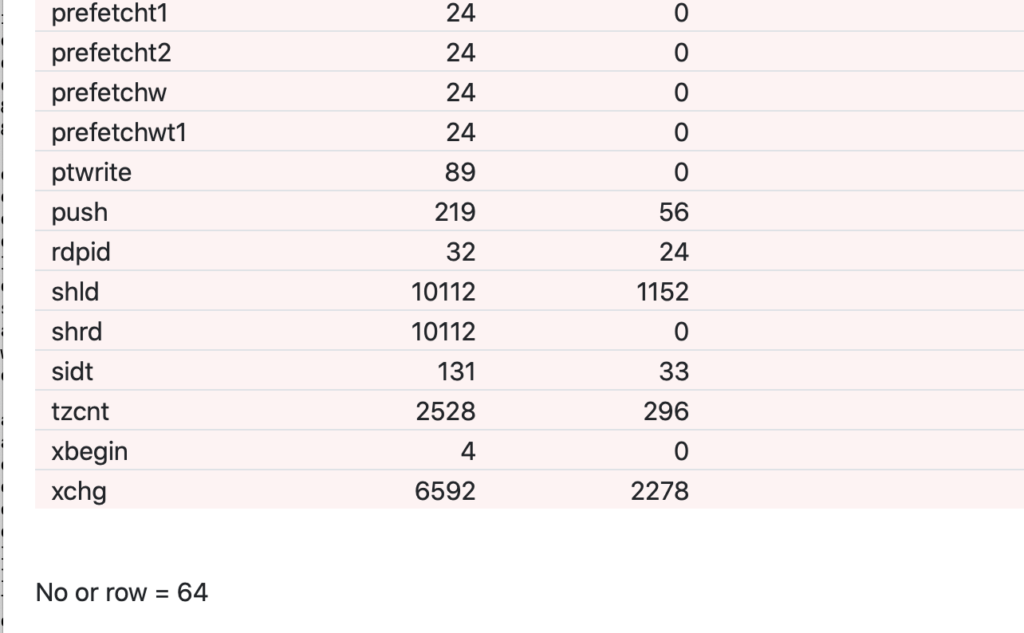

As usual, meet in Festival Walk, sync-ed up our verilog skill, stuck in the "imm | label" to grammar. Only 64 instructions left. 2020/02/16

RISC-V要implement哂所有concept是有難度的

2020/02/14