Category Archives: Soft core cpu

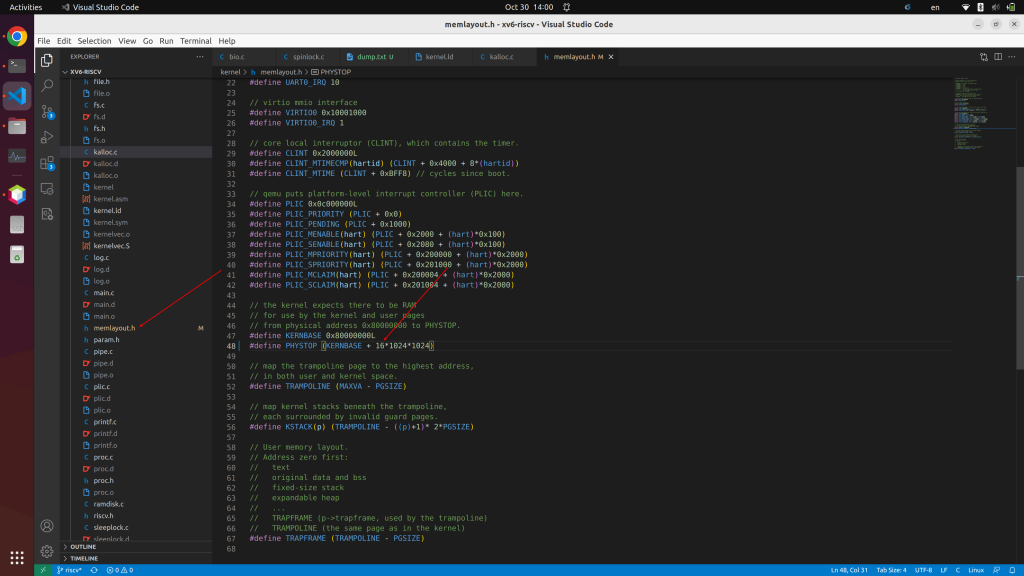

Change qemu to use 16M ram for xv6-riscv

After testing, the minimal memory of xv6-riscv needed is 3MB 2022/10/30

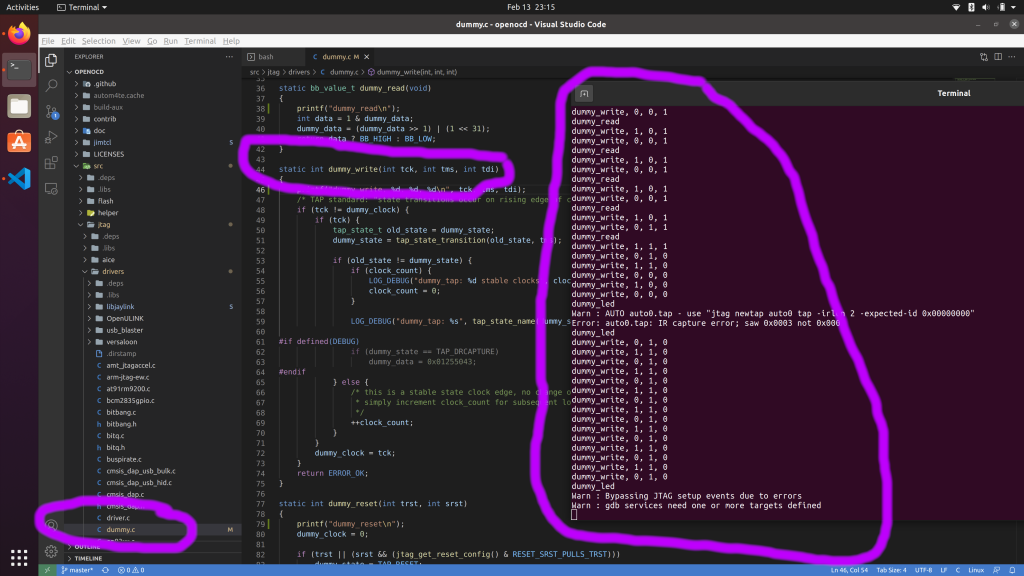

start point to build our own jtag for our risc-v cpu

After days of hacking, i finally found out there is a dummy driver in openocd. just ./configure --enable-dummy and run it by ./bin/openocd -c 'interface dummy' -c 'adapter_khz 1' , you can see the dummy driver is running and in the function "static int dummy_write(int tck, int tms, int tdi)", we can manually toggle the […] 2022/02/13

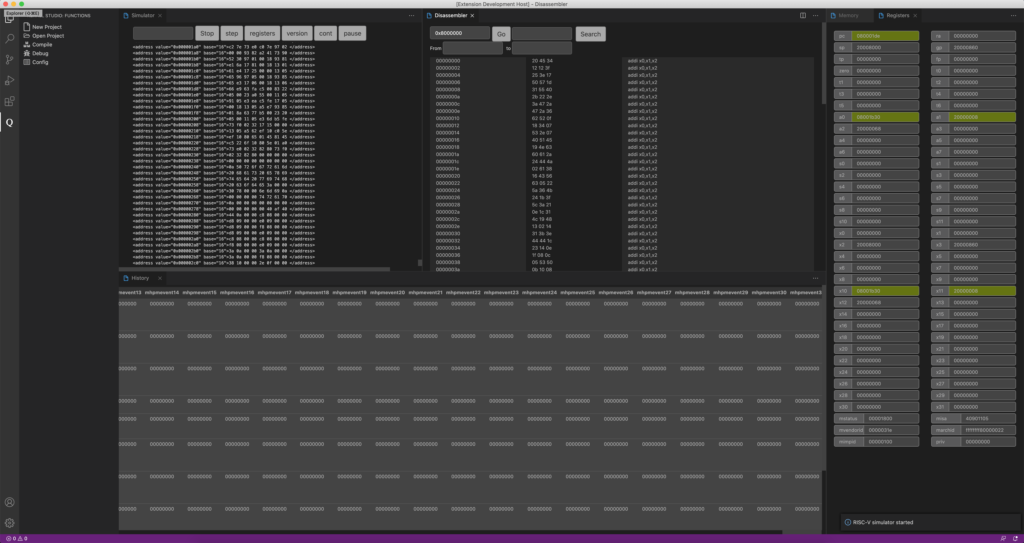

Our RISC-V simulator interface

2020/10/29

Hacking Lattice toolchain lesson 1

Lattice Diamond use these commands to compile my project into jed file Synthesize Design: synthesis -f ControlLed_impl1_lattice.synproj -gui -msgset C:/workspace/fpga/ControlLed/promote.xml Place & Route Design: par -w -l 5 -i 6 -t 1 -c 0 -e 0 -gui -msgset C:/workspace/fpga/ControlLed/promote.xml -exp parUseNBR=1:parCDP=0:parCDR=0:parPathBased=OFF ControlLed_impl1_map.ncd ControlLed_impl1.dir/5_1.ncd ControlLed_impl1.prf trce -v 10 -gt -sethld -sp 4 -sphld m -o ControlLed_impl1.twr […] 2019/11/27

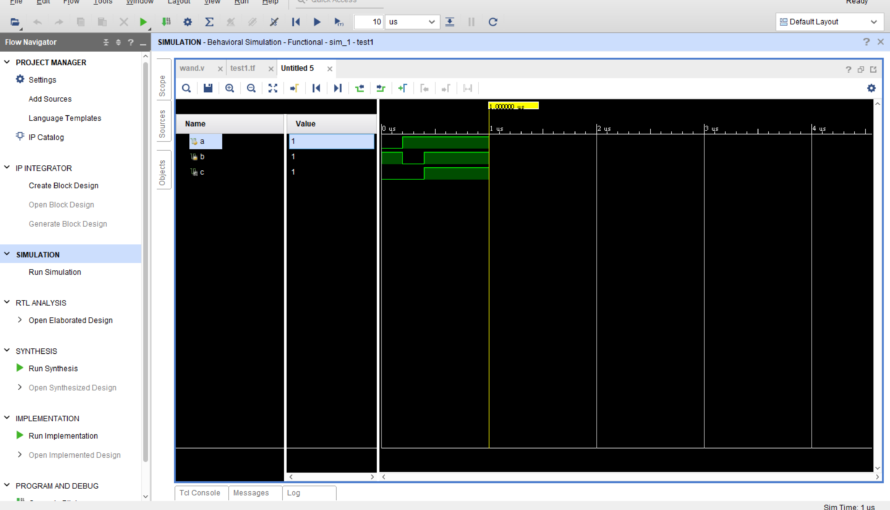

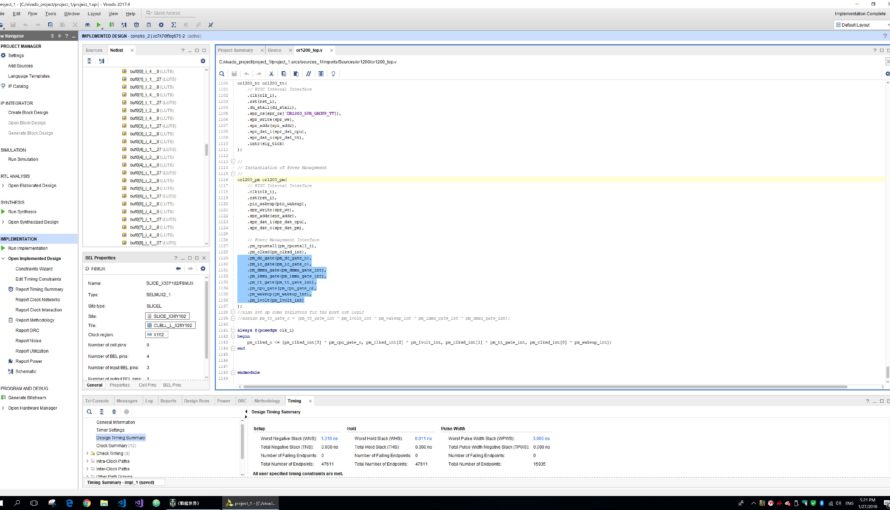

Can write simple test bench in vivado

After reading my verilog book for few days, i can write test bench file to test my verilog program in vivado. I like vivado much more than altera quartus, the UI is much more clean. 2018/02/02

For the user interface, Vivado is much nicer than Quartus

For the user interface, Vivado is much nicer than Quartus. Better to stick into Xilinux to build my soft core. 2018/01/27